EFFICIENT EUCLIDEAN DISTANCE CALCULATIONS AND DISTANCE

SIMILARITY SEARCHES: AN EXAMINATION OF HETEROGENEOUS CPU, GPU,

AND TENSOR CORE ARCHITECTURES

By Benoît Gallet

A Dissertation

Submitted in Partial Fulfillment

of the Requirements for the Degree of

Doctor of Philosophy

in Informatics and Computing

Northern Arizona University

May 2023

Approved:

Michael Gowanlock, Ph.D., Chair

Frédéric Loulergue, Ph.D.

Toby Hocking, Ph.D.

Dieter Otte, Ph.D.

Yiqi Luo, Ph.D.

## ABSTRACT

# EFFICIENT EUCLIDEAN DISTANCE CALCULATIONS AND DISTANCE SIMILARITY SEARCHES: AN EXAMINATION OF HETEROGENEOUS CPU, GPU, AND TENSOR CORE ARCHITECTURES

BENOÎT GALLET

The Euclidean distance is a measure frequently used in numerous applications, including data-analysis algorithms, to determine the similarity between objects, as a function of the distance between them. Given a set of objects, performing a distance similarity search consists of finding objects that are considered similar, i.e., finding objects within a threshold search distance of a given object, where the distance measure often employs the Euclidean distance formula. Distance similarity searches can be used as a building block for other algorithms, including the distance similarity join, *k*-Nearest Neighbors (*k*-NN), *k*-Means, or the Density-Based Spatial Clustering of Applications with Noise (DBSCAN) algorithms. As such, optimizing the computation of Euclidean distances will improve the performance of distance similarity searches, and improving distance similarity searches will improve the performance of numerous other algorithms. Consequently, optimizing both Euclidean distance calculations and distance similarity searches is critical to improve the performance of many data-analysis algorithms, including the ones mentioned above, in addition to applications in other domains such as fields that require modeling and simulation.

The literature is rich with methods to improve the performance of Euclidean distance calculations and distance similarity searches, particularly using Central Processing Units (CPUs). While multicore CPUs can offer great parallel performance, they are outclassed by the higher computational throughput of Graphics Processing Units (GPUs). Using GPUs for these problems is relatively recent and there are, consequently, significantly fewer proposed work that use the GPU instead of the CPU. However, the design space for GPU algorithms is large, thus some algorithm designs have been neglected, including those that carefully exploit GPU resources. Furthermore, while both CPUs and GPUs have been extensively studied

on their own, very little work has been conducted where both architectures are leveraged concurrently.

Tensor Cores (TCs) are a recent addition to certain GPU architectures. As an Application-Specific Integrated Circuit (ASIC), TCs are designed to compute Matrix Multiply-Accumulate (MMA) operations, at a higher throughput than other general-purpose cores. In the literature, TCs are primarily used for machine learning and other related fields involving linear algebra, yielding great performance improvements. Despite their specificity, TCs can be leveraged for any algorithm where the computation can be expressed using MMA operations. Nevertheless, leveraging TCs for general-purpose scientific algorithms remains an open problem.

We propose in this dissertation to optimize the performance of Euclidean distance calculations and more generally distance similarity searches, by examining: *(i)* GPU resource utilization; *(ii)* the joint use of both CPUs and GPUs for computation; *(iii)* the use of TCs to compute Euclidean distances; *(iv)* the joint use of general-purpose GPU cores and TCs to compute Euclidean distances.

## ACKNOWLEDGEMENTS

First and foremost, I would like to show my gratitude to my supervisor, Michael Gowanolock. He helped and supported me even before starting this Ph.D., never stopped since, and always provided me with incredibly valuable advice. I am very grateful and glad I got to be his student and to learn from him. Thank you for accepting to be my supervisor from the beginning and until the end!

I would then like to thank the members of my committee: Frédéric Louergue, Toby Hocking, Dieter Otte, and Yiqi Luo for accepting this task in the first place, for reading this manuscript, and for their very useful recommendations on how to make it better.

Many thanks to all the people I have befriended while in Flagstaff, including my previous and current housemates. There are too many of you to name everyone individually, but know that your support and the time spent with you all these years were extremely appreciated, and sometimes even needed!

Finally, I would like to thank Ciarán, whom I only met this year but who is already important to me, and who greatly supported me in this last stretch. Thank you for being there, and I hope that you will be by my side for a long time.

## REMERCIEMENTS

J'aimerais tout d'abord remercier Frédéric Loulergue sans qui toute cette aventure n'aurait tout simplement pas été possible. D'Orléans à Flagstaff, c'est grâce à lui que j'en suis ici aujourd'hui. Merci également pour les précieux conseils au fil des années et au moment de la relecture de ce manuscrit.

J'aimerais ensuite remercier ma famille, et plus particulièrement ma mère ainsi que mon beau-père pour leur soutien depuis l'autre côté du globe. Maman, je me souviendrai toujours de ce samedi matin où je vous ai annoncé que j'étais accepté dans ce programme, et que j'allais partir plusieurs années à des milliers de kilomètres. Tes mots ont été "*ton père aurait été fier de toi*". Je l'espère, et j'espère que vous l'êtes aussi. Merci également à mes frères, ma sœur ainsi que ma grand-mère.

À Emmanuel et Martin, merci pour ces années passées à vos côtés, les projets de l'université, votre soutien, et les innombrables heures à jouer ensemble (peut-être même trop !).

Et pour conclure ces remerciements: Jolan, présent depuis le début. Le lycée, l'université, Flagstaff. Tu es à mes côtés depuis de nombreuses années à m'aider, me soutenir, à vivre des aventures que je n'oublierai jamais. En particulier la première année à Flagstaff ! Anthony et Ana, également présents depuis des années déjà. Chaque moment avec vous est fantastique, inattendu, et toujours mémorable. Merci pour votre soutien, vos encouragements, ainsi que les aventures vécues et à venir.

Je ne pourrais pas rêver d'une meilleure famille et de meilleurs amis que ce que j'ai. Je vous aime.

## Table of Contents

|                                                       |             |

|-------------------------------------------------------|-------------|

| <b>Abstract</b>                                       | <b>ii</b>   |

| <b>Acknowledgements</b>                               | <b>iv</b>   |

| <b>Remerciements</b>                                  | <b>v</b>    |

| <b>List of Tables</b>                                 | <b>xi</b>   |

| <b>List of Figures</b>                                | <b>xv</b>   |

| <b>List of Abbreviations and Definitions</b>          | <b>xxii</b> |

| <b>Preface</b>                                        | <b>xxvi</b> |

| <b>1 Introduction</b>                                 | <b>1</b>    |

| 1.1 Motivations . . . . .                             | 4           |

| 1.2 Challenges . . . . .                              | 5           |

| 1.3 Contributions . . . . .                           | 6           |

| 1.4 Outline . . . . .                                 | 7           |

| <b>2 Background and Related Work</b>                  | <b>8</b>    |

| 2.1 Euclidean Distance . . . . .                      | 8           |

| 2.2 Distance Similarity Searches . . . . .            | 9           |

| 2.3 Task and Data Parallelism . . . . .               | 10          |

| 2.4 CPU Architecture . . . . .                        | 11          |

| 2.5 GPU Architecture . . . . .                        | 12          |

| 2.5.1 GPU Tensor Cores . . . . .                      | 14          |

| 2.6 Comparison of CPU and GPU Architectures . . . . . | 16          |

| 2.7 Heterogeneous Computing . . . . .                 | 17          |

|                                                                                                    |           |

|----------------------------------------------------------------------------------------------------|-----------|

| <b>3 Load Imbalance Mitigation Optimizations for GPU-Accelerated Similarity Joins</b>              | <b>19</b> |

| 3.1 Introduction . . . . .                                                                         | 20        |

| 3.2 Background . . . . .                                                                           | 22        |

| 3.2.1 Problem Statement . . . . .                                                                  | 22        |

| 3.2.2 Related Work . . . . .                                                                       | 23        |

| 3.2.3 Overview of Leveraged Previous Work . . . . .                                                | 25        |

| 3.3 Mitigating Load Imbalance . . . . .                                                            | 29        |

| 3.3.1 Increasing the Granularity of each Range Query . . . . .                                     | 30        |

| 3.3.2 Cell Access Pattern: Linear ID Unidirectional Comparison . . . . .                           | 32        |

| 3.3.3 Local and Global Load Balancing: Sorting by Workload . . . . .                               | 33        |

| 3.3.4 Forcing the Warp Execution Order using a Work Queue . . . . .                                | 34        |

| 3.4 Experimental Evaluation . . . . .                                                              | 36        |

| 3.4.1 Datasets . . . . .                                                                           | 36        |

| 3.4.2 Methodology . . . . .                                                                        | 37        |

| 3.4.3 Results . . . . .                                                                            | 38        |

| 3.5 Discussion and Conclusion . . . . .                                                            | 44        |

| <b>4 Heterogeneous CPU-GPU Epsilon Grid Joins: Static and Dynamic Work Partitioning Strategies</b> | <b>47</b> |

| 4.1 Introduction . . . . .                                                                         | 48        |

| 4.2 Background . . . . .                                                                           | 53        |

| 4.2.1 Problem Statement . . . . .                                                                  | 53        |

| 4.2.2 GPU Architecture . . . . .                                                                   | 54        |

| 4.2.3 Related Work . . . . .                                                                       | 54        |

| 4.3 Leveraged Work . . . . .                                                                       | 59        |

| 4.3.1 GPU Algorithm: LBJOIN . . . . .                                                              | 59        |

| 4.3.2 CPU Algorithm: SUPER-EGO . . . . .                                                           | 62        |

| 4.4 Heterogeneous CPU-GPU Algorithm: HEGJOIN . . . . .                                             | 63        |

| 4.4.1 Shared Work Queue . . . . .                                                                  | 63        |

| 4.4.2 Workload Partitioning . . . . .                                                              | 65        |

|          |                                                                                         |           |

|----------|-----------------------------------------------------------------------------------------|-----------|

| 4.4.3    | Batching Scheme: Complying with Non-Increasing Workload . . . . .                       | 73        |

| 4.4.4    | GPU Component: HEGJOIN-GPU . . . . .                                                    | 74        |

| 4.4.5    | CPU Component: HEGJOIN-CPU . . . . .                                                    | 75        |

| 4.5      | Experimental Evaluation . . . . .                                                       | 76        |

| 4.5.1    | Selectivity . . . . .                                                                   | 76        |

| 4.5.2    | Datasets . . . . .                                                                      | 76        |

| 4.5.3    | Methodology . . . . .                                                                   | 77        |

| 4.5.4    | Results . . . . .                                                                       | 79        |

| 4.5.5    | Discussion . . . . .                                                                    | 94        |

| 4.6      | Conclusion . . . . .                                                                    | 97        |

| <b>5</b> | <b>Leveraging GPU Tensor Cores for Double Precision Euclidean Distance Calculations</b> | <b>99</b> |

| 5.1      | Introduction . . . . .                                                                  | 100       |

| 5.2      | Background . . . . .                                                                    | 103       |

| 5.2.1    | Problem Statement . . . . .                                                             | 103       |

| 5.2.2    | Tensor Cores (TCs) . . . . .                                                            | 103       |

| 5.2.3    | Tensor Cores in the Literature . . . . .                                                | 105       |

| 5.2.4    | Distance Similarity Joins . . . . .                                                     | 106       |

| 5.3      | Distance Calculations using Tensor Cores . . . . .                                      | 108       |

| 5.3.1    | Adapting the Euclidean Distance Formula . . . . .                                       | 108       |

| 5.3.2    | Tensor Cores for Distance Similarity Joins . . . . .                                    | 111       |

| 5.4      | Experimental Evaluation . . . . .                                                       | 113       |

| 5.4.1    | Datasets . . . . .                                                                      | 113       |

| 5.4.2    | Methodology . . . . .                                                                   | 114       |

| 5.4.3    | Results: Comparison of Brute-force TC Approaches . . . . .                              | 116       |

| 5.4.4    | Results: Optimized TC and CUDA Core Approaches . . . . .                                | 118       |

| 5.4.5    | Discussion: When Tensor Cores Should Be Employed . . . . .                              | 121       |

| 5.5      | Conclusion and Future Work . . . . .                                                    | 125       |

|                                                                                              |            |

|----------------------------------------------------------------------------------------------|------------|

| <b>6 Optimizing Euclidean Distance Calculations in Low Precision with GPU Tensor Cores</b>   | <b>128</b> |

| 6.1 Introduction . . . . .                                                                   | 129        |

| 6.2 Background . . . . .                                                                     | 131        |

| 6.2.1 Problem Statement . . . . .                                                            | 131        |

| 6.2.2 Tensor Cores (TCs) . . . . .                                                           | 132        |

| 6.2.3 Tensor Cores in the Literature . . . . .                                               | 133        |

| 6.2.4 Case Study: Distance Similarity Searches . . . . .                                     | 134        |

| 6.2.5 TCs Distance Similarity Searches . . . . .                                             | 135        |

| 6.3 Mixed-Precision Euclidean Tensor cores Algorithm (META) . . . . .                        | 136        |

| 6.3.1 META-1Q Algorithm . . . . .                                                            | 137        |

| 6.3.2 META-16Q Algorithm . . . . .                                                           | 138        |

| 6.3.3 META-16Q and FP16 . . . . .                                                            | 139        |

| 6.3.4 META Memory Layout . . . . .                                                           | 140        |

| 6.3.5 Using META for Distance Similarity Self-Joins . . . . .                                | 141        |

| 6.4 Experimental Evaluation . . . . .                                                        | 142        |

| 6.4.1 Datasets . . . . .                                                                     | 142        |

| 6.4.2 Methodology . . . . .                                                                  | 143        |

| 6.4.3 Brute-Force Performance . . . . .                                                      | 144        |

| 6.4.4 Dataset Reordering Performance . . . . .                                               | 146        |

| 6.4.5 Catastrophic Cancellation . . . . .                                                    | 147        |

| 6.4.6 Accuracy of FP16, FP16-FP32, and FP64 . . . . .                                        | 148        |

| 6.4.7 Algorithm Performance Comparisons . . . . .                                            | 150        |

| 6.5 Discussion and Conclusion . . . . .                                                      | 151        |

| <b>7 Discussion &amp; Conclusion</b>                                                         | <b>156</b> |

| 7.1 Summary of Contributions . . . . .                                                       | 157        |

| 7.1.1 Load Imbalance Mitigation Optimizations for GPU-Accelerated Similarity Joins . . . . . | 157        |

|       |                                                                                                     |            |

|-------|-----------------------------------------------------------------------------------------------------|------------|

| 7.1.2 | Heterogeneous CPU-GPU Epsilon Grid Joins: Static and Dynamic Work Partitioning Strategies . . . . . | 159        |

| 7.1.3 | Leveraging GPU Tensor Cores for Double Precision Euclidean Distance Calculations . . . . .          | 161        |

| 7.1.4 | Optimizing Euclidean Distance Calculations in Low Precision with GPU Tensor Cores . . . . .         | 162        |

| 7.2   | Future Perspectives . . . . .                                                                       | 162        |

| 7.2.1 | Further Tensor Core Optimizations . . . . .                                                         | 162        |

| 7.2.2 | Heterogeneous CUDA-Tensor Euclidean Distance Calculations . . . . .                                 | 163        |

| 7.2.3 | Performance Modeling of Euclidean Distance Calculations for CUDA and Tensor Cores . . . . .         | 163        |

| 7.2.4 | Exploring Novel Architecture Features . . . . .                                                     | 164        |

|       | <b>Bibliography</b>                                                                                 | <b>166</b> |

## List of Tables

|     |                                                                                                                                                                                                                                                      |    |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Available standard floating-point precisions and matrix sizes of matrices $A, B, C$ and $D$ using the WMMA API [78]. . . . .                                                                                                                         | 15 |

| 2.2 | Comparison of the Intel Xeon Platinum 8358 CPU [52, 53] and Nvidia A100 GPU [73] architectures and performance, both processors equipping the Leonardo supercomputer [89]. . . . .                                                                   | 16 |

| 3.1 | Summary of the different datasets used for the experimental evaluation. $ D $ denotes the number of points and $n$ the dimensionality. . . . .                                                                                                       | 37 |

| 3.2 | Optimizations and notation used throughout the evaluation. . . . .                                                                                                                                                                                   | 38 |

| 3.3 | Warp execution efficiency (WEE) of the GPUCALCGLOBAL kernel as well as the UNICOMP and LID-UNICOMP cell access patterns over our synthetic datasets and for specific values of $\epsilon$ . The time corresponds to that in Figure 3.9. . . . .      | 39 |

| 3.4 | Warp execution efficiency (WEE) of the GPUCALCGLOBAL with $k = 1$ and when $k = 8$ on synthetic datasets and for specific values of $\epsilon$ . The time corresponds to that in Figure 3.10. . . . .                                                | 41 |

| 3.5 | Warp execution efficiency (WEE) of the GPUCALCGLOBAL kernel, as well as the SORTBYWL and WORKQUEUE optimizations on our synthetic datasets and for specific values of $\epsilon$ . The time corresponds to that in Figure 3.11. . . . .              | 43 |

| 3.6 | Warp execution efficiency (WEE) of the GPUCALCGLOBAL, the WORKQUEUE, and the WORKQUEUE combined with LID-UNICOMP and $k = 8$ on our real world datasets and for specific values of $\epsilon$ . The time corresponds to that in Figure 3.12. . . . . | 45 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.1 | Summary of the different properties of HEGJOIN-DYN, HEGJOIN-SQ, and HEGJOIN-SC. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 73  |

| 4.2 | Summary of the datasets used to conduct our experiments. $ D $ denotes the number of points, $d$ the dimensionality, and $S$ the selectivity range for the values of $\epsilon$ we use. The <i>Expo</i> - datasets are exponentially distributed synthetic datasets (using $\lambda = 40$ ), while the others are real-world datasets. . . . .                                                                                                                                                                                                                           | 77  |

| 4.3 | Comparison of the number of candidate points refined by LBJOIN vs. NEW-SUPER-EGO, and ratio of the number of candidate points refined by LBJOIN over the number of candidate points refined by NEW-SUPER-EGO on a selection of our datasets (Table 4.2). Results from Platform 1. . . . .                                                                                                                                                                                                                                                                                | 82  |

| 4.4 | Throughput of candidate points refined (candidates/s) by LBJOIN, NEW-SUPER-EGO, the upper bound of LBJOIN plus NEW-SUPER-EGO, HEGJOIN-DYN, and the performance ratio between HEGJOIN-DYN and the upper bound across several datasets. Results from Platform 1. . . . .                                                                                                                                                                                                                                                                                                   | 89  |

| 4.5 | Total time taken by data transfers between the CPU and the GPU, the total execution time of the algorithm, and the upper bound overhead ratio of the data transfers time to the execution time when using HEGJOIN-DYN. A ratio close to zero indicates an insignificant overhead incurred by data transfers compared to the total execution time. The ratios do not account for the periods of time where the data transfers and the kernel executions overlap. The times were recorded on the Nvidia Visual Profiler over a single time trial using Platform 2. . . . . | 93  |

| 5.1 | Synthetic datasets used in the experimental evaluation. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 114 |

| 5.2 | Real-world datasets used in the experimental evaluation. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 114 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.3 | L1 and L2 cache hit rates of GDS-JOIN and TED-JOIN on a selection of exponentially distributed synthetic datasets ( $2 \leq d \leq 16$ , $n = 2M$ ) and real-world datasets (SW3DA and SuSy), measured using the Nvidia Nsight Compute profiler. . . . .                                                                                                                                                            | 124 |

| 5.4 | Average and maximum speedup of TED-JOIN over SUPER-EGO, FGF-HILBERT, and GDS-JOIN across experiments reported in Figures 5.7 and 5.8. . . . .                                                                                                                                                                                                                                                                       | 124 |

| 6.1 | Exponentially distributed synthetic datasets used in the experimental evaluation. . . . .                                                                                                                                                                                                                                                                                                                           | 142 |

| 6.2 | Real-world datasets used in the experimental evaluation. . . . .                                                                                                                                                                                                                                                                                                                                                    | 142 |

| 6.3 | Summary of implementation names across different levels of precision. The suffixes are as follows: “hh” refers to multiplication and accumulation in FP16, “hs” refers to multiplication in FP16 and accumulation in FP32, and “dd” refers to multiplication and accumulation in FP64. . . . .                                                                                                                      | 143 |

| 6.4 | Profiling results of brute-force GDS-JOIN, META-1Q and META-16Q using mixed FP16-FP32 computation on the $2^{20}$ points 64-D synthetic dataset. . . . .                                                                                                                                                                                                                                                            | 146 |

| 6.5 | Example of the catastrophic cancellation problem when computing the distance between the first point from the <i>SuSy</i> dataset (Table 6.2) and itself. . . . .                                                                                                                                                                                                                                                   | 148 |

| 6.6 | Accuracy ratio of the GDS-JOIN, META-1Q and META-16Q algorithms as compared to the result of GDS-JOIN using FP64 when computing the distance similarity self-join. The percentage $p = (1 - ( R_{ref}  -  R_{comp} ) /  R_{ref} ) * 100$ where $R_{ref}$ is the result set (the set of result pairs) returned by GDS-JOIN using FP64 and $R_{comp}$ is the result set returned by the comparison algorithm. . . . . | 149 |

| 6.7 | Minimum, maximum and average speedup of META-1Q and META-16Q vs. GDS-JOIN using mixed FP16-FP32 precision, as well as GDS-JOIN and TED-JOIN using FP64, on the same selection of datasets as shown in Figure 6.5.151                                                                                                                                                                                                | 151 |

|                                                                                                                                                                                               |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.1 Summary of the contributions of this dissertation, sorted by processor (CPU/GPU)<br>and by examined algorithm: Distance Similarity Searches (DSS) or Euclidean<br>Distances (ED). . . . . | 158 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

## List of Figures

|                                                                                                                                                                                                                                                                                                                                                                      |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

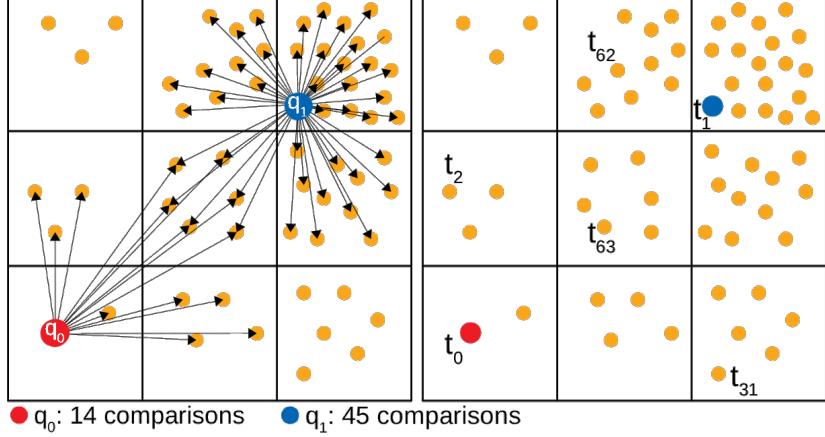

| 3.6 Illustration of the load imbalance between query points and therefore between threads, where $q_0$ and $q_1$ are two query points and $t_0$ and $t_1$ two threads processing the query points $q_0$ and $q_1$ respectively. . . . .                                                                                                                              | 34 |

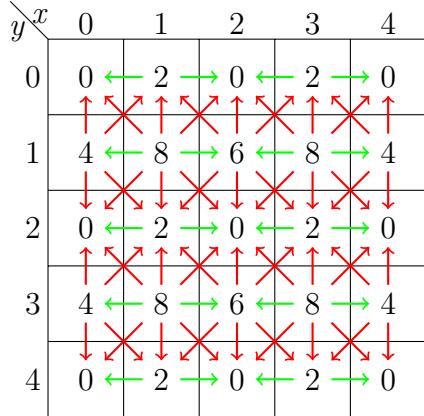

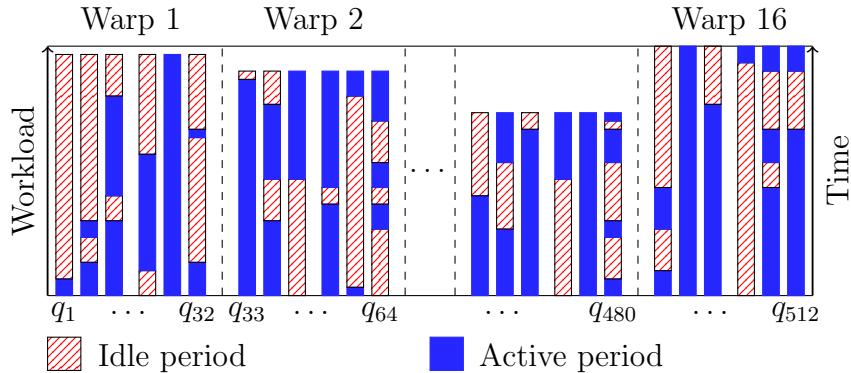

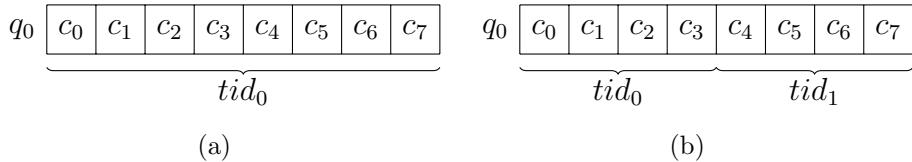

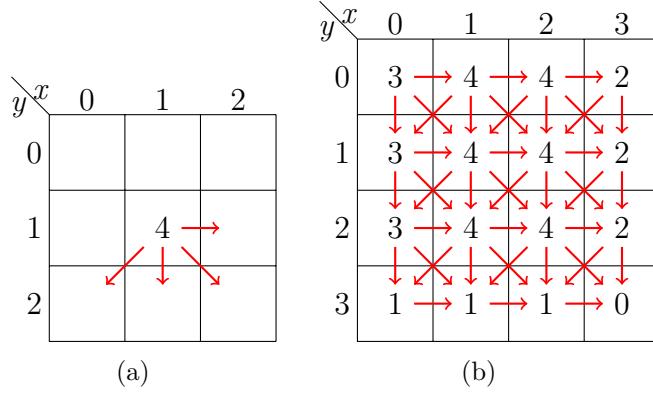

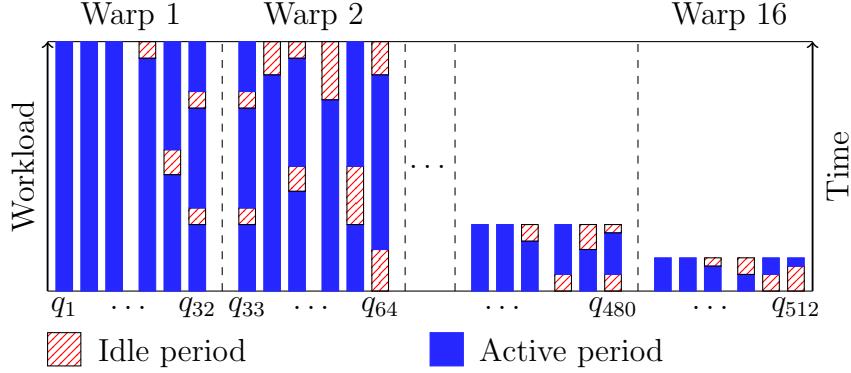

| 3.7 Representation of balancing the workload between the threads within the same warp. We use for this example a dataset $D = 512$ . . . . .                                                                                                                                                                                                                         | 35 |

| 3.8 Representation of the points' execution order when using the WORKQUEUE optimization. $D'$ is the sorted dataset, and $W$ gives the workload of each query point. The first 32 points with the most workload will be executed at the beginning within the same warp, while the last 32 points, with the least workload, will be executed at the very end. . . . . | 35 |

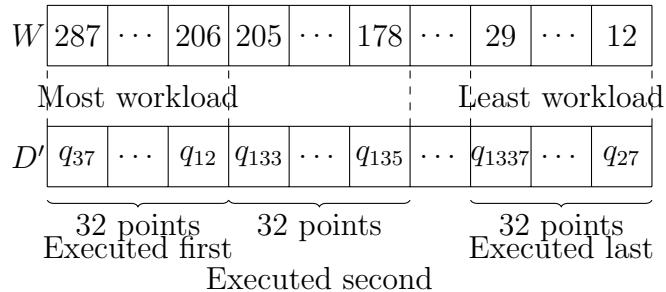

| 3.9 Response times of the LID-UNICOMP cell access pattern, versus the GPU-CALCGLOBAL kernel and the UNICOMP cell access pattern on our synthetic datasets. The legend in (a) is used across all subfigures, and we set $k = 1$ . . . . .                                                                                                                             | 39 |

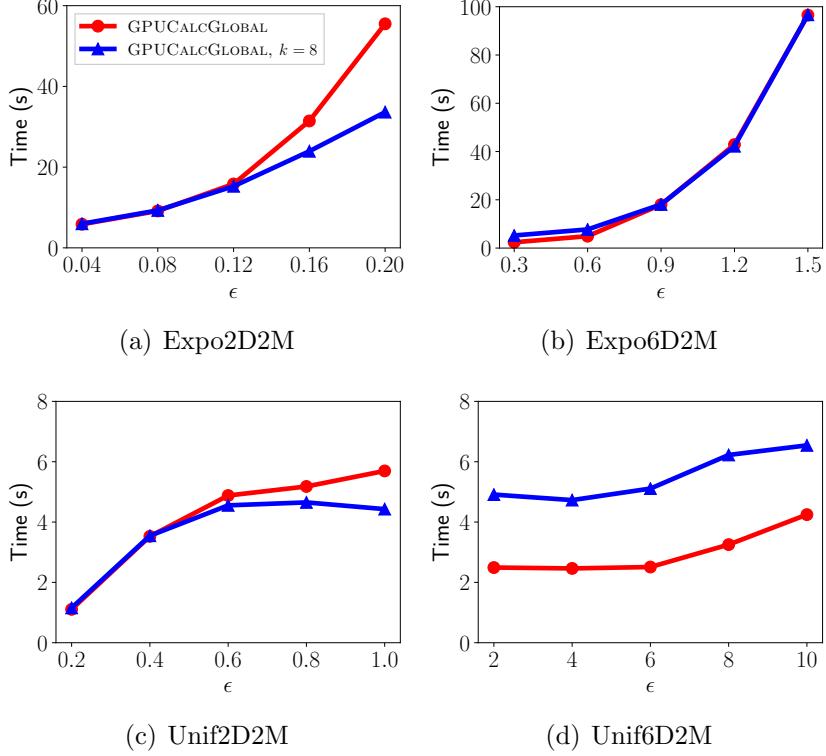

| 3.10 Response time of the increase of the granularity when $k = 8$ versus $k = 1$ for the GPU CALCGLOBAL kernel on our synthetic datasets. The legend in (a) is used across all subfigures. . . . .                                                                                                                                                                  | 41 |

| 3.11 Response time of the SORTBYWL and WORKQUEUE optimizations against the GPU CALCGLOBAL kernel on our synthetic datasets. The legend in (a) is used across all subfigures, and we set $k = 1$ . . . . .                                                                                                                                                            | 42 |

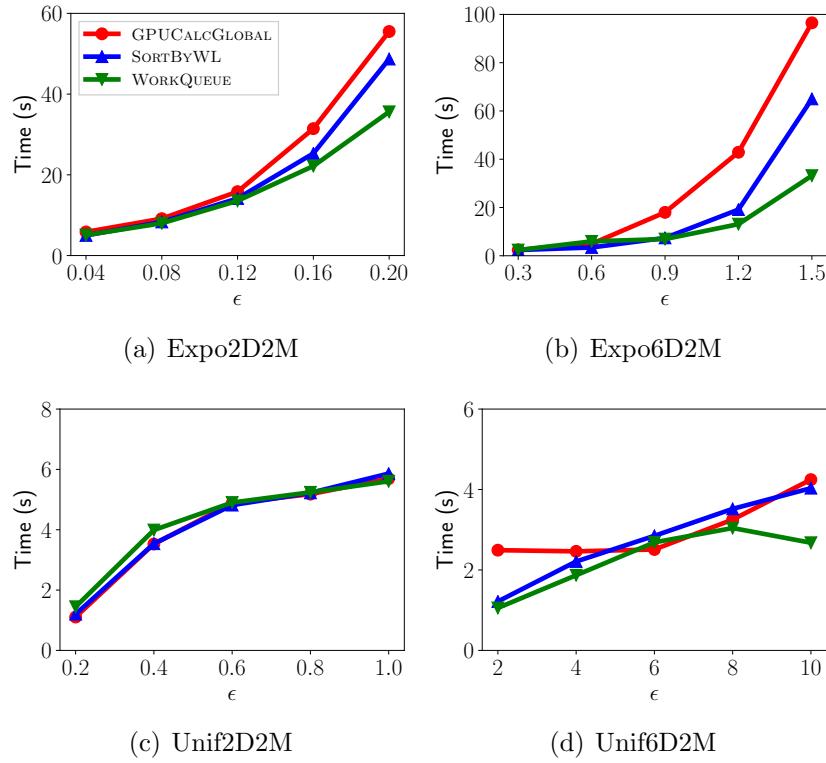

| 3.12 Response time vs. $\epsilon$ on real world datasets of the WORKQUEUE optimization, the WORKQUEUE combined with the LID-UNICOMP pattern, the WORKQUEUE with $k = 8$ , and both combined to the WORKQUEUE compared to the GPU-CALCGLOBAL kernel and the SUPER-EGO CPU parallel algorithm. The legend in the subfigure (a) is used across all subfigures. . . . .  | 44 |

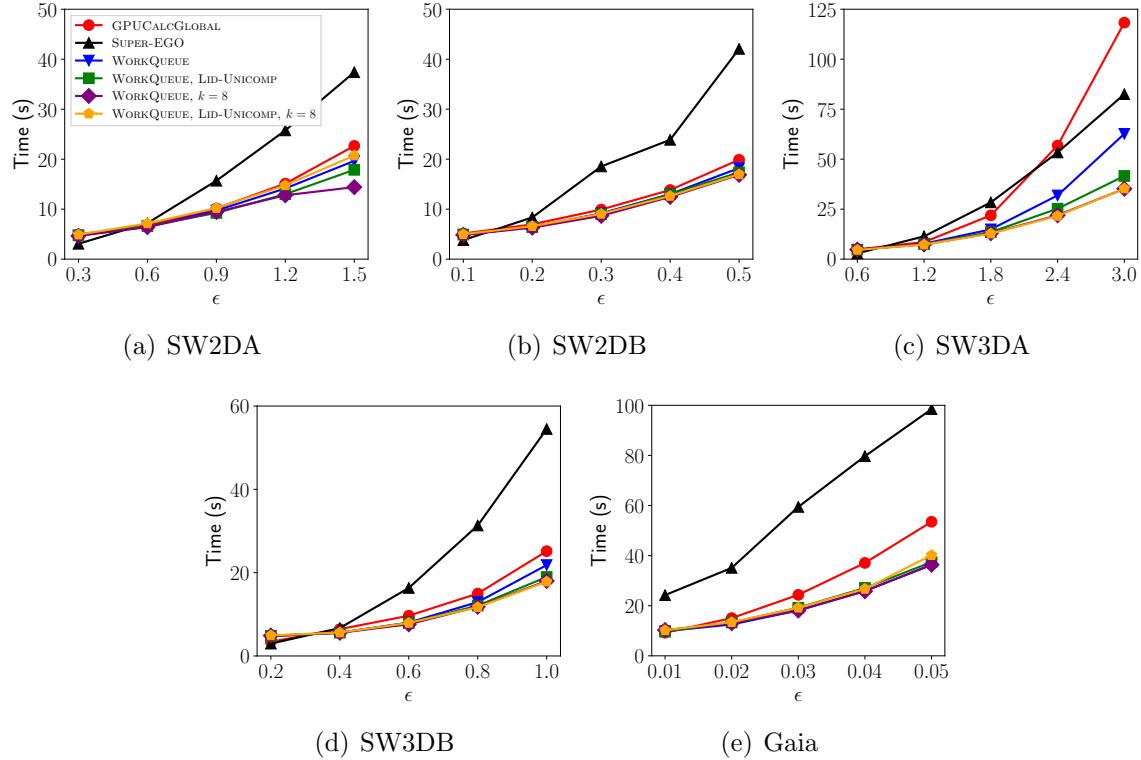

| 3.13 Speedup of the WORKQUEUE combined to LID-UNICOMP and $k = 8$ optimization against the SUPER-EGO parallel algorithm (a), and over the GPU-CALCGLOBAL kernel (b), on several datasets. $\epsilon$ values are plotted on a log scale to observe all data points. . . . .                                                                                           | 46 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.1 | Representation of how we combine SUPER-EGO and LBJOIN by using a single work queue to form HEGJOIN. When using the static partitioning strategy, the CPU and the GPU would access the work queue only once (at the beginning of the algorithm to retrieve their assigned queries). When using the dynamic partitioning scheme, the CPU and the GPU would iteratively query the work queue for queries to compute until it is empty. . . . .                                                                                                                                                                                                                                                                                                  | 51 |

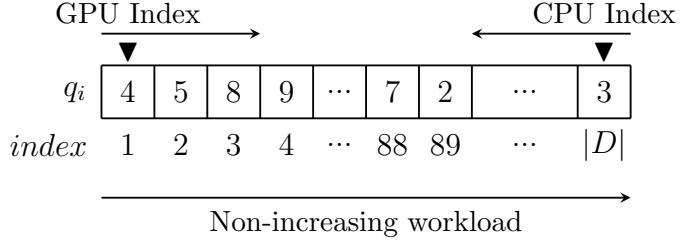

| 4.2 | Representation of our deque as an array. The numbers $q_i$ are the query points id, the triangles are the starting position of each index, and the arrows above it indicate the indices progression in the deque. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 64 |

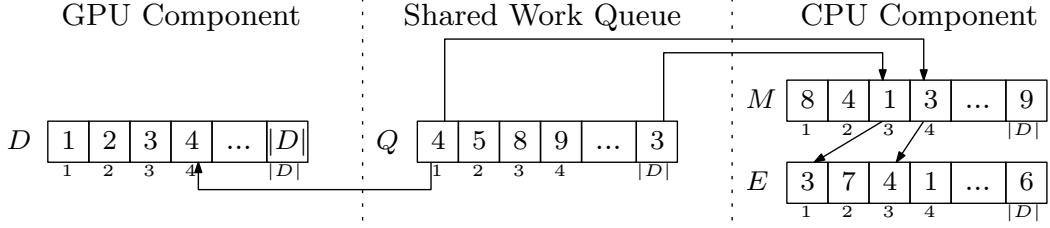

| 4.3 | Illustration of an input dataset $D$ , the shared deque sorted by workload $Q$ , the input dataset EGO-sorted $E$ and the mapping $M$ between $Q$ and $E$ . The numbers in $D$ , $Q$ , and $E$ correspond to query point ids, while the numbers in $M$ correspond to their position in $E$ . The numbers below the arrays are the indices of the elements. . . . .                                                                                                                                                                                                                                                                                                                                                                           | 65 |

| 4.4 | Representation of the static partitioning strategy based on the query points, where $D$ is the dataset sorted by workload, $i$ refers to the indices of the query points in $D$ , and $W_{est}$ the workload of the points using the equal workload assumption and that is determined by our model (and where $w_{est}^{total}$ is the estimated workload of HEGJOIN). As we use the equal workload assumption, each query point is therefore assigned the same workload. Furthermore, we consider in this example that the model considers the CPU and GPU to have the same throughput, and thus assigns the same estimated workload to both processors ( $w_{est}^{CPU} = w_{est}^{GPU}$ ), i.e., the same number of query points. . . . . | 67 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.5 Representation of the static partitioning strategy based on the candidate points, where $D$ is the dataset, $i$ the indices of the query points in $D$ , the workload of the points $w$ as used to sort them by their workload (and where $w^{Total}$ is the total number of candidate points to refine), and $w_{est}$ the workload of the query points determined by the model (and where $w_{est}^{total}$ is the total estimated workload of HEGJOIN). While we consider for this example that the model estimates a workload that is equal to the workload of HEGJOIN ( $w_{est}^{total} = w^{Total}$ ), there might be scenarios in which $w_{est}^{total}$ and $w^{Total}$ are different. We consider in this example that the model estimates the CPU and GPU to have the same throughput, and thus assign the same number of estimated candidate points to refine to the CPU and to the GPU ( $w_{est}^{CPU} = w_{est}^{GPU}$ ). Furthermore, as in this example the estimated workload is the same as the actual workload of HEGJOIN ( $w_{est}^{total} = w^{Total}$ ), both processors are assigned the same amount of work to compute ( $w^{GPU} = w^{CPU}$ ), i.e., the same number of candidate points to refine. . . . . | 70 |

| 4.6 Representation of the new batch estimator. The bold numbers are the estimated number of neighbors of those points, while the other numbers are inferred, based on the maximum result between the two closest estimated points shown in bold. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 73 |

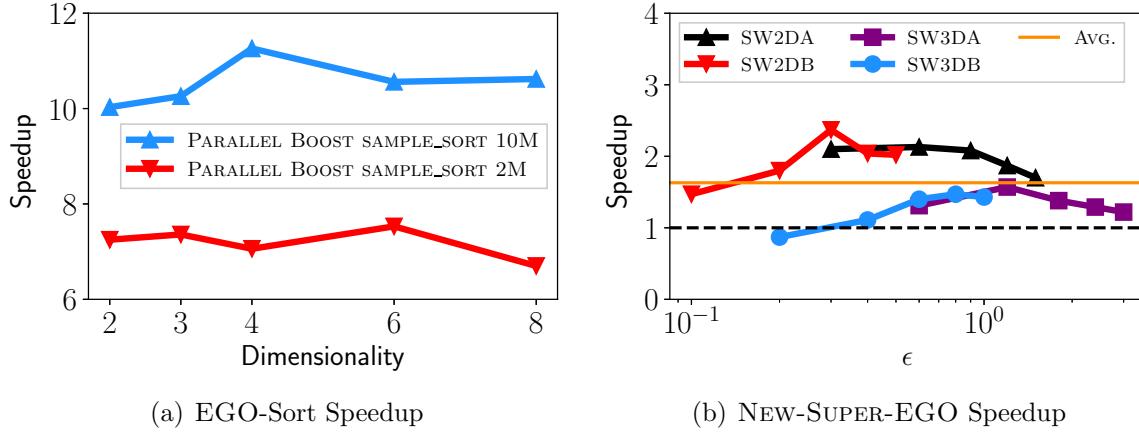

| 4.7 (a) Speedup to EGO-Sort our exponentially distributed synthetic datasets using SAMPLE_SORT from the Boost library over QSORT from the C standard library. $S = 0\text{--}9.39K$ and $S = 0\text{--}1.99K$ on the 2M and 10M points datasets, respectively. (b) Speedup of NEW-SUPER-EGO over SUPER-EGO on the SW- real-world datasets. Results from Platform 1. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 81 |

|                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

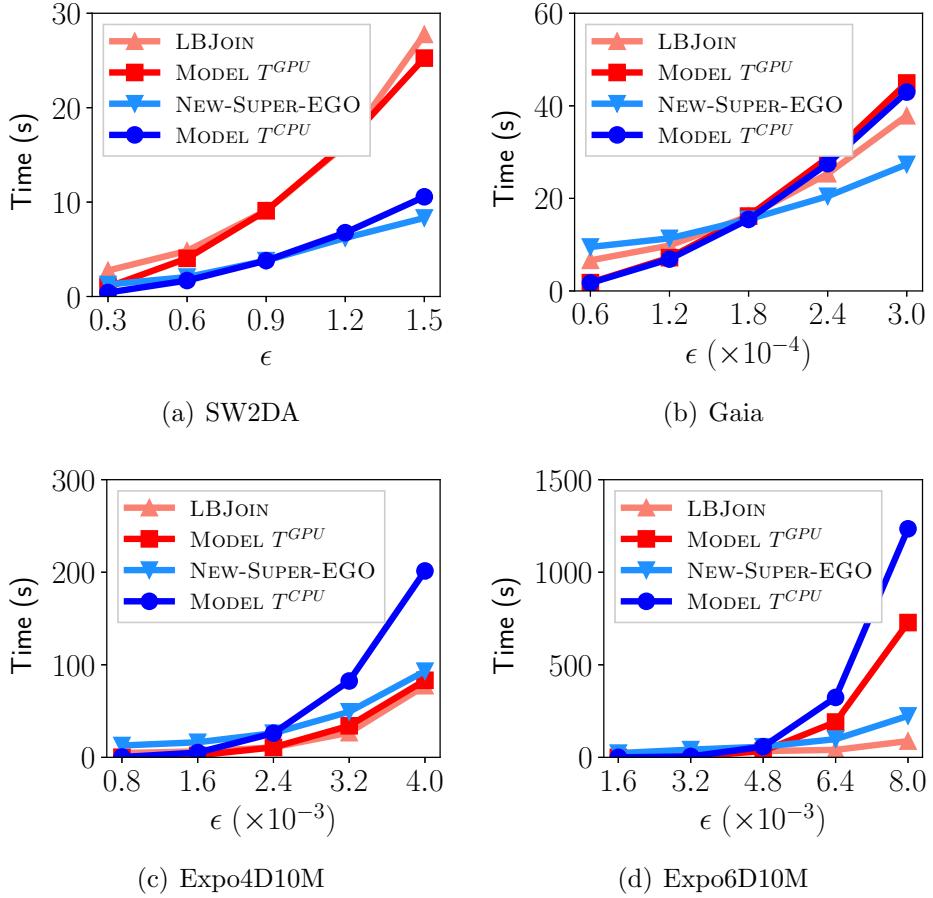

| 4.8 Comparison of the modeled execution times $T^{GPU}$ and $T^{CPU}$ vs. their corresponding reference execution times LBJOIN and NEW-SUPER-EGO on a selection of datasets: (a) <i>SW2DA</i> , (b) <i>Gaia</i> , (c) <i>Expo4D10M</i> and (d) <i>Expo6D10M</i> . Results from Platform 1. . . . .                                                                                                                          | 83 |

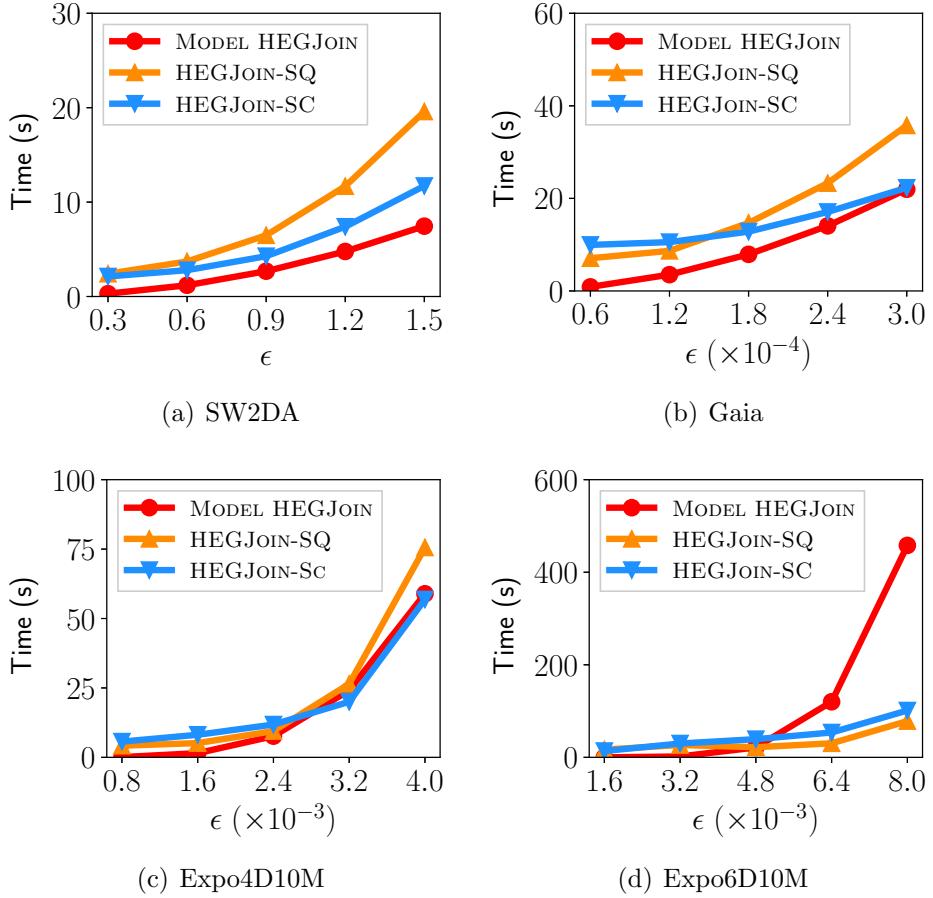

| 4.9 Comparison of the modeled execution time of HEGJOIN as determined by the static partitioning model vs. the response time of HEGJOIN-SQ and HEGJOIN-SC on a selection of datasets: (a) <i>SW2DA</i> , (b) <i>Gaia</i> , (c) <i>Expo4D10M</i> and (d) <i>Expo6D10M</i> . Results from Platform 1. . . . .                                                                                                                 | 84 |

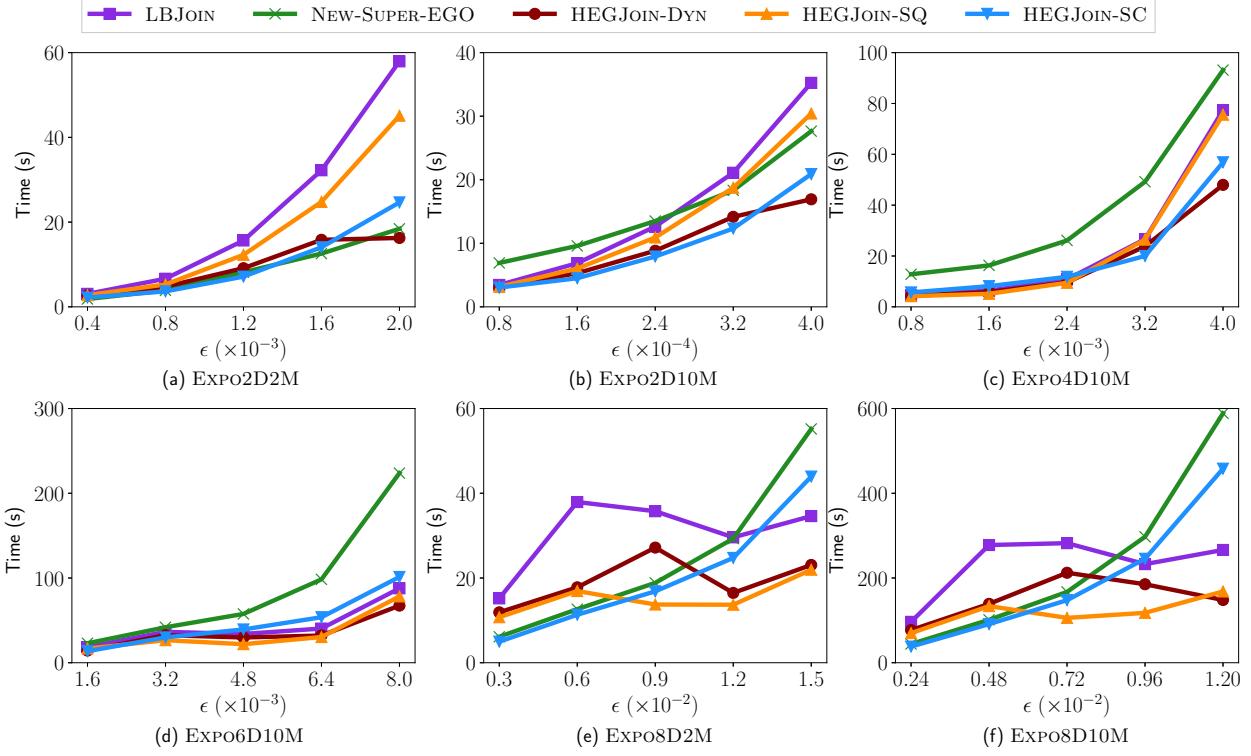

| 4.10 Response time of HEGJOIN-DYN, HEGJOIN-SQ, HEGJOIN-SC, LBJOIN and NEW-SUPER-EGO on (a) <i>Expo2D2M</i> , (b) <i>Expo2D10M</i> , (c) <i>Expo4D10M</i> , (d) <i>Expo6D10M</i> , (e) <i>Expo8D2M</i> , and (f) <i>Expo8D10M</i> . $S$ is in the range (a) 397–9.39K, (b) 80–1.99K, (c) 3–1.63K, (d) 0–499, (e) 0–157, and (f) 0–167. Results from Platform 1. . . . .                                                      | 86 |

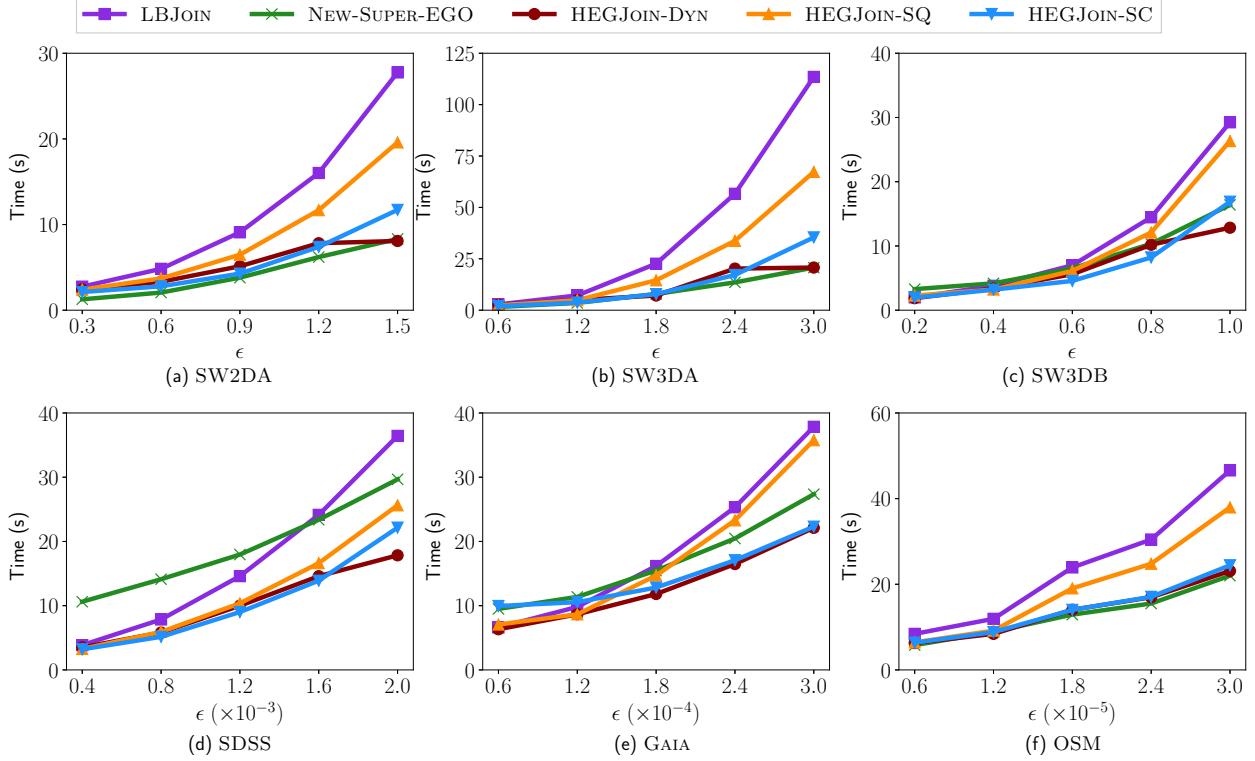

| 4.11 Response time of HEGJOIN-DYN, HEGJOIN-SQ, HEGJOIN-SC, LBJOIN and NEW-SUPER-EGO on (a) <i>SW2DA</i> , (b) <i>SW3DA</i> , (c) <i>SW3DB</i> , (d) <i>SDSS</i> , (e) <i>Gaia</i> , and (f) <i>OSM</i> . $S$ is in the range (a) 295–5.82K, (b) 239–13.2K, (c) 33–2.13K, (d) 1–31, (e) 19–455, and (f) 67–571. Results from Platform 1. . .                                                                                 | 88 |

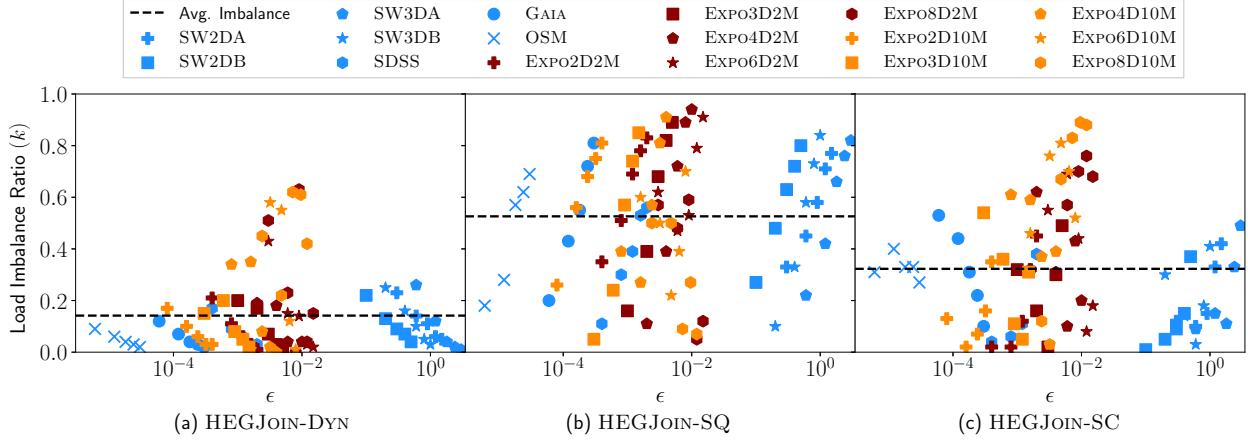

| 4.12 Load imbalance ratio of (a) HEGJOIN-DYN, (b) HEGJOIN-SQ and (c) HEGJOIN-SC on all the datasets we use for our experiments, and we described in Table 4.2. The horizontal dashed line corresponds to the average load imbalance $k$ , and is as follows: (a) $k = 0.14$ , (b) $k = 0.53$ and (c) $k = 0.32$ . Results from Platform 1. . . . .                                                                          | 90 |

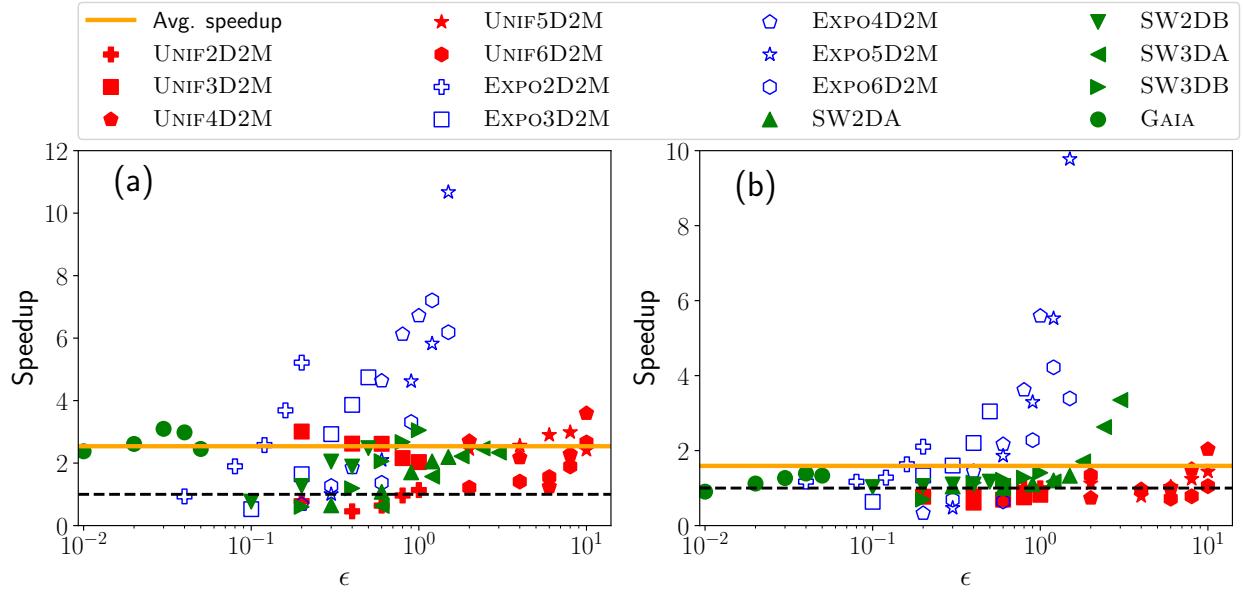

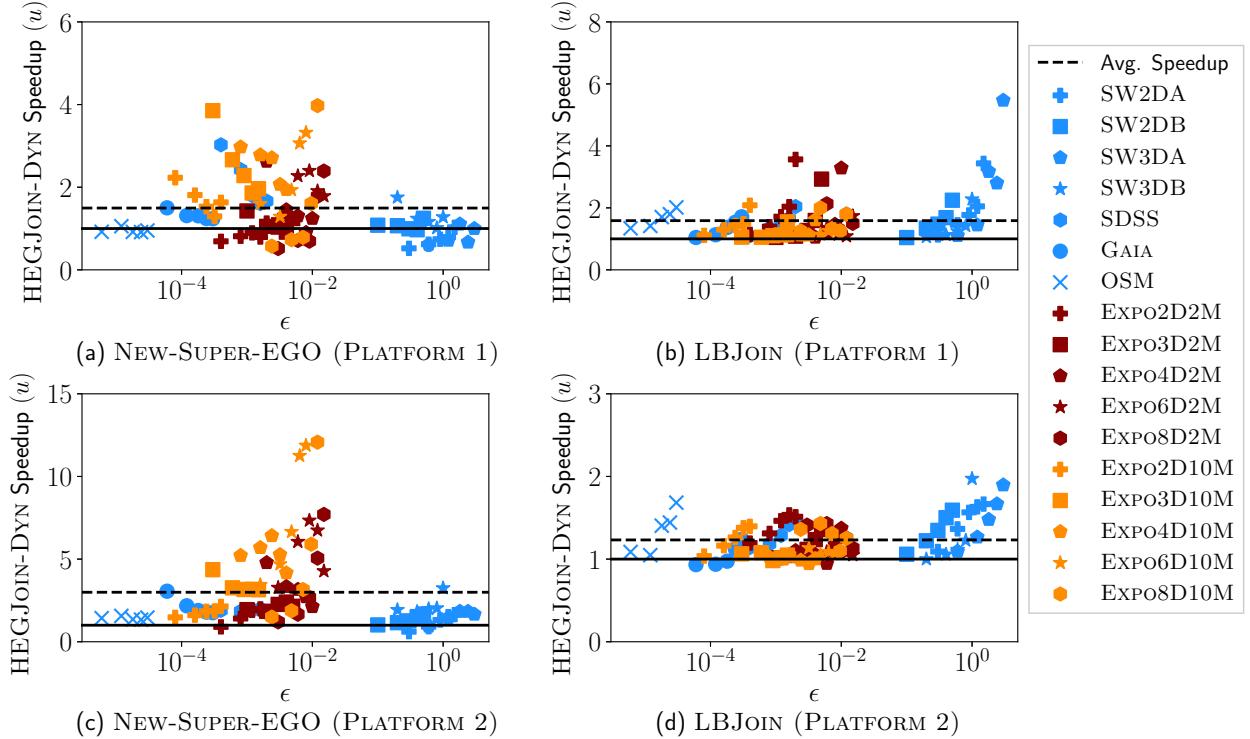

| 4.13 Average speedup of HEGJOIN-DYN over (a) NEW-SUPER-EGO and (b) LBJOIN on Platform 1, and over (c) NEW-SUPER-EGO and (d) LBJOIN on Platform 2, across all datasets (Table 4.2). The horizontal dashed line corresponds to the average speedup $u$ , and is as follows: (a) $u = 1.50$ , (b) $u = 1.59$ , (c) $u = 2.99$ , and (d) $u = 1.23$ . The horizontal solid line corresponds to a speedup of $u = 1.0$ . . . . . | 96 |

|     |                                                                                                                                                                                                                                                                                                                                           |     |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.1 | Illustration of Euclidean distance calculations using TCs and Equation 5.2, between a point $a$ and four points $e, f, g, h$ , and in four dimensions. This computation is computed in blocking fashion four dimensions at a time. Matrix $D$ contains the Euclidean distance between $a$ and the other points. . . . .                   | 108 |

| 5.2 | Illustration of Euclidean distance calculations using TCs and Equation 5.3, between four points $a, b, c, d$ and four points $e, f, g, h$ , and in four dimensions. This computation is computed in blocking fashion four dimensions at a time. Matrix $D$ contains the Euclidean distances between $a, b, c, d$ and $e, f, g, h$ . . . . | 111 |

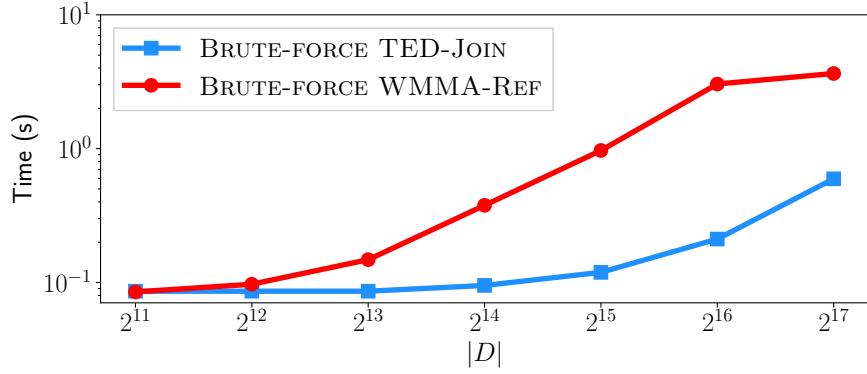

| 5.3 | Response time of our proposed algorithm TED-JOIN, and WMMA-REF an optimized MMA algorithm from Nvidia leveraging the WMMA API, using brute-force searches to compute Euclidean distance calculations on a 16-D exponentially distributed synthetic datasets. . . . .                                                                      | 118 |

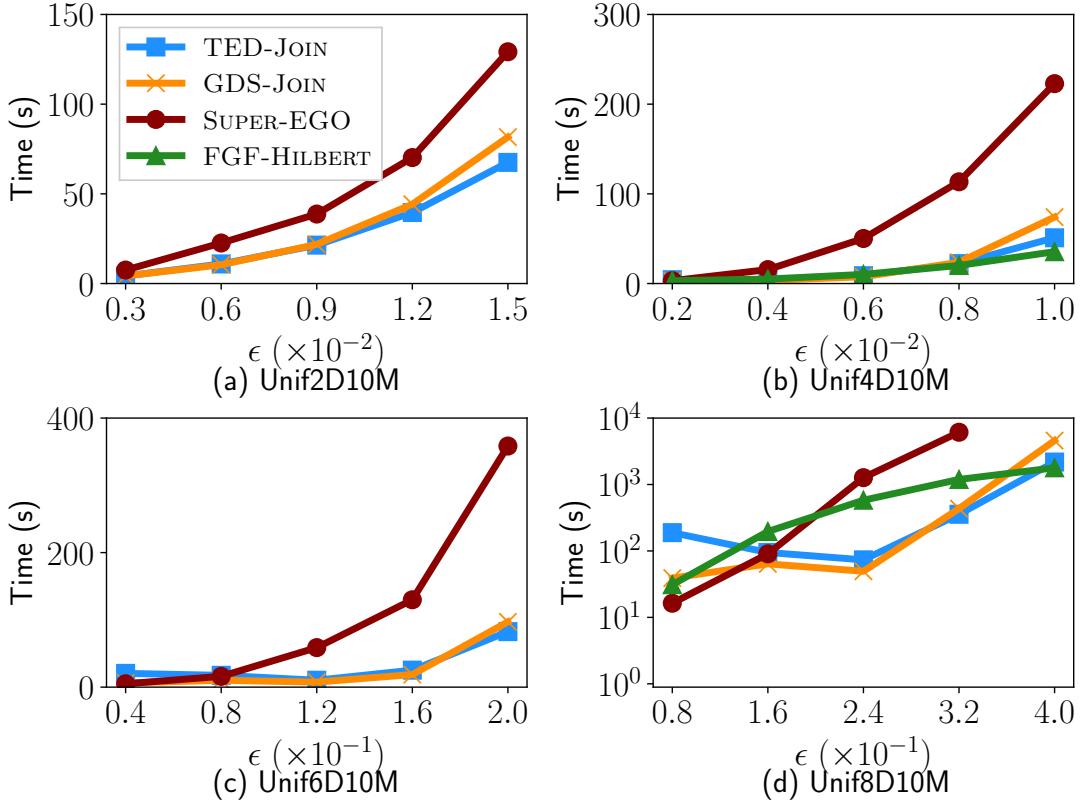

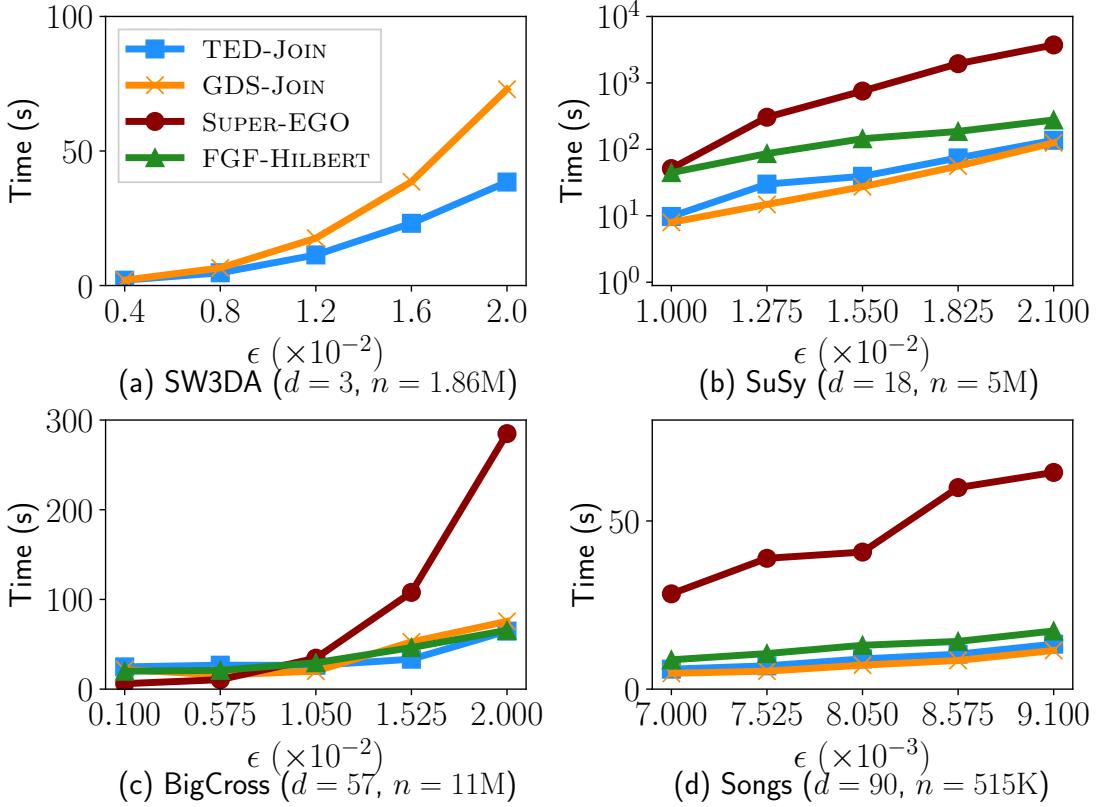

| 5.4 | Response times of the TED-JOIN, GDS-JOIN, SUPER-EGO, and FGF-HILBERT on a selection of uniformly distributed synthetic datasets. $s$ is in the range (a) 282–6978, (b) 71–8449, (c) 7–4295 and (d) 0–10888. The legend in (a) corresponds to all subfigures. $d \in \{2, 4, 6, 8\}$ , $n = 10M$ . . . . .                                 | 119 |

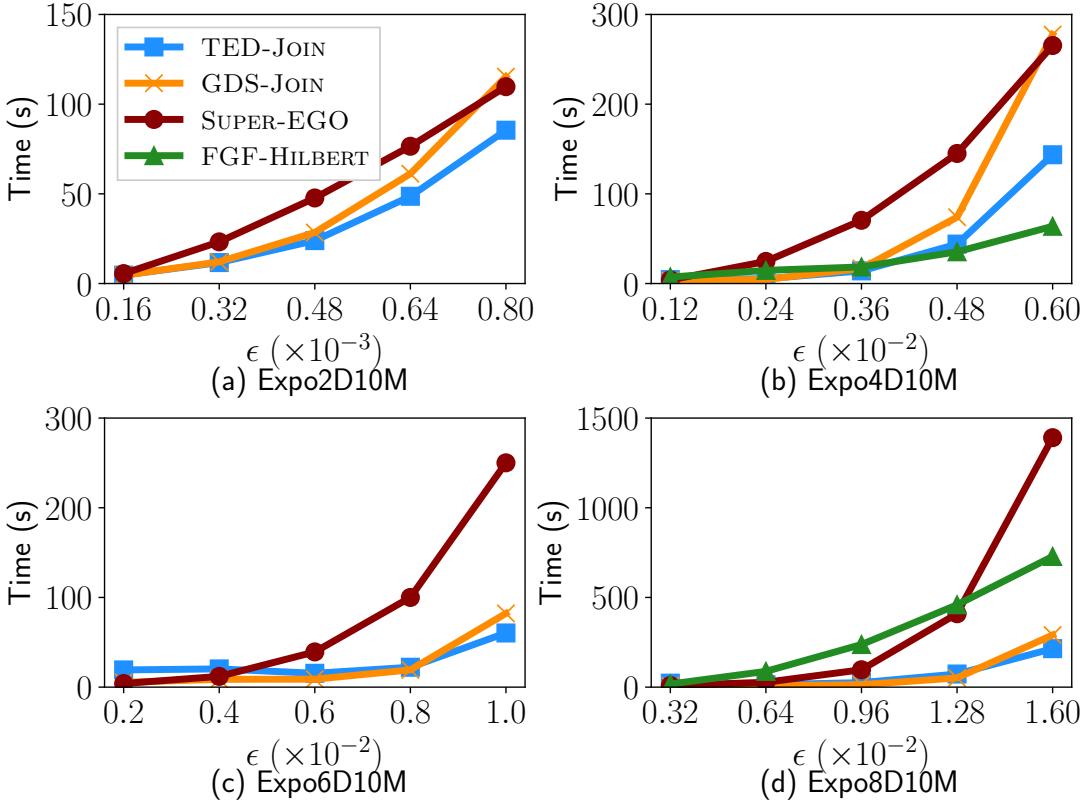

| 5.5 | Response times of TED-JOIN, GDS-JOIN, SUPER-EGO, and FGF-HILBERT on a selection of exponentially distributed synthetic datasets. $s$ is in the range (a) 320–7834, (b) 15–7414, (c) 0–1658 and (d) 0–1210. The legend in (a) corresponds to all subfigures. $d \in \{2, 4, 6, 8\}$ , $n = 10M$ . . . . .                                  | 121 |

| 5.6 | Response times of TED-JOIN, GDS-JOIN, SUPER-EGO, and FGF-HILBERT on a selection of real-world datasets (Table 5.2). $s$ is in the range (a) 163–5373, (b) 5–1090, (c) 1–1104 and (d) 127–998. The legend in (a) corresponds to all subfigures. . . . .                                                                                    | 122 |

|                                                                                                                                                                                                                                                                                                                                                                     |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

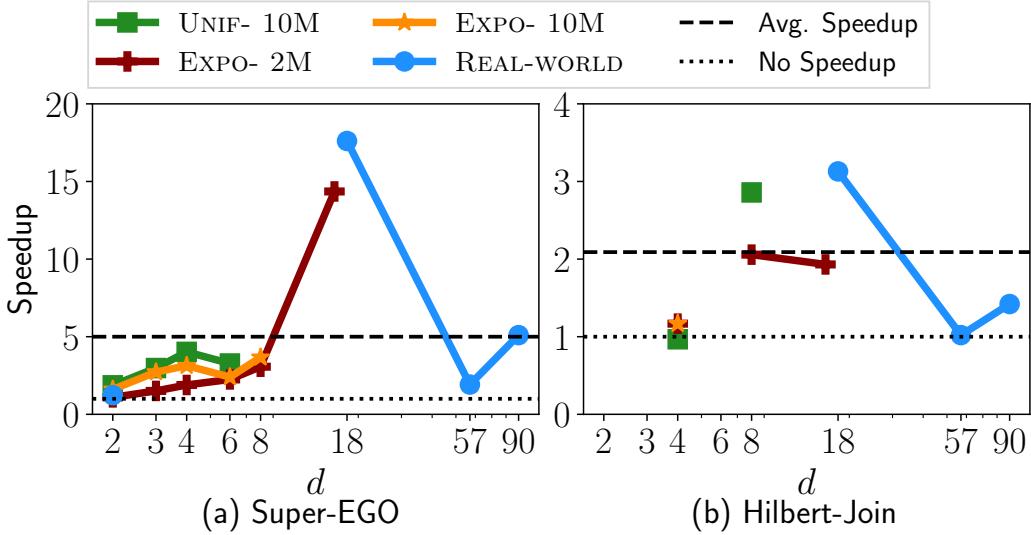

| 5.7 Speedups of TED-JOIN over (a) SUPER-EGO and (b) FGF-HILBERT across datasets presented in Tables 5.1 and 5.2, for all values of $\epsilon$ we used, and as a function of the dimensionality. The dashed horizontal lines correspond to the average speedups of TED-JOIN over a compared algorithm, and the dotted horizontal lines represent no speedup. . . . . | 123 |

| 5.8 The same as for Figure 5.7, but plotting the speedup of TED-JOIN over GDS-JOIN. . . . .                                                                                                                                                                                                                                                                         | 123 |

| 6.1 Illustration of Euclidean distance calculations for the META-1Q and META-16Q algorithms presented below (Sections 6.3.1 and 6.3.2). Reproduced and modified from Gallet and Gowanlock [38]. While we show $4 \times 4$ matrices for illustration purposes, META-1Q and META-16Q use $16 \times 16$ matrices. . .                                                | 136 |

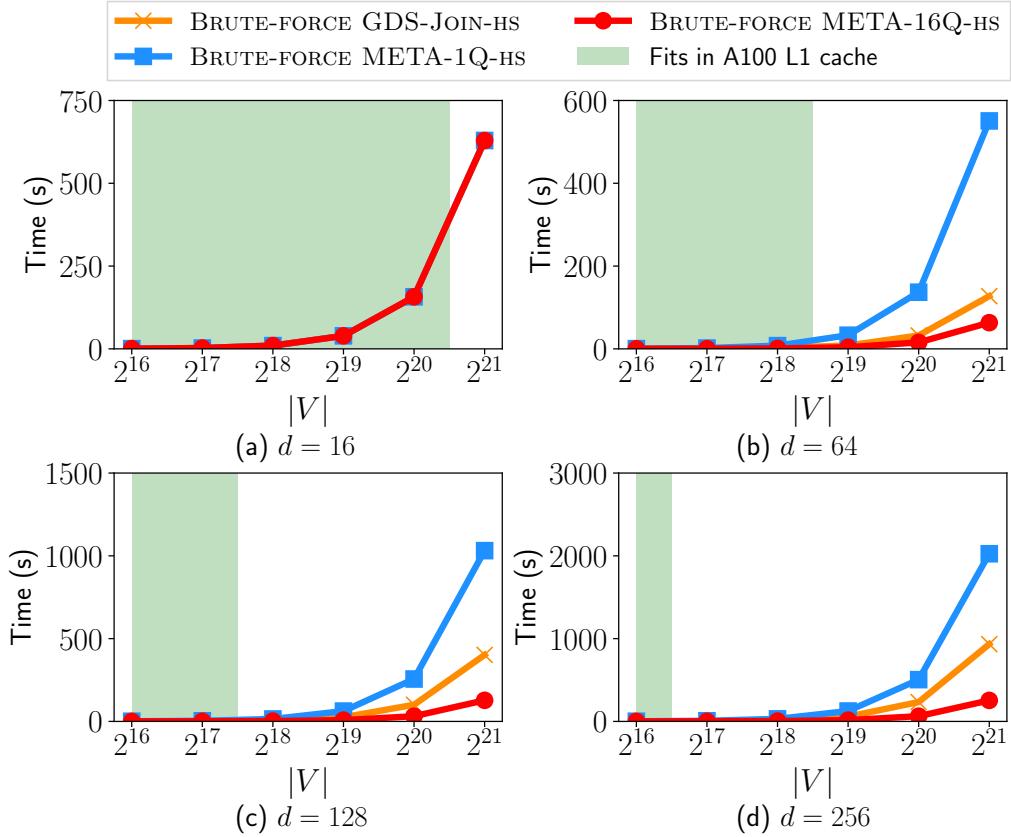

| 6.2 Response time of META-1Q and META-16Q versus GDS-JOIN, using brute-force searches to compute Euclidean distance calculations on a selection of exponentially distributed synthetic datasets and as a function of the dataset size $ V $ . The computation uses mixed FP16-FP32 precision. . . . .                                                               | 145 |

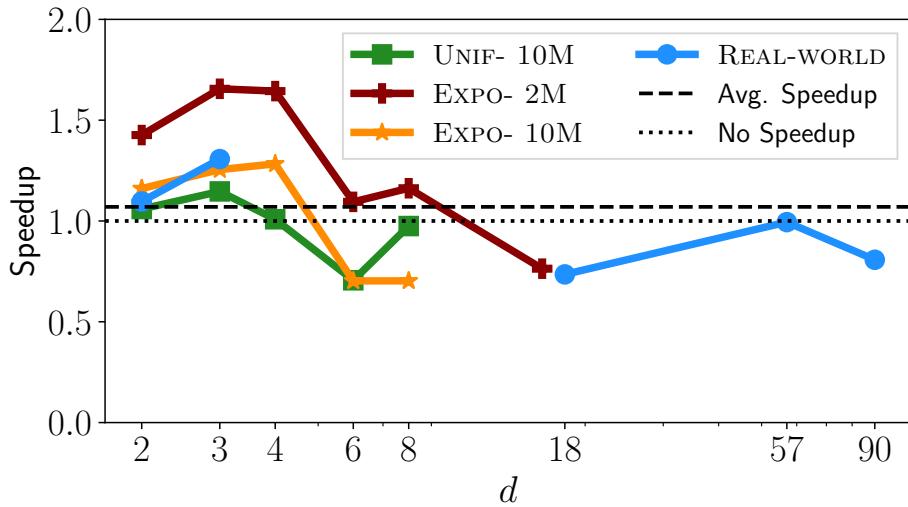

| 6.3 Speedup of META-1Q, META-16Q and GDS-JOIN using the reordering dataset optimization, and using mixed FP16-FP32 precision on a selection of exponentially distributed synthetic datasets. . . . .                                                                                                                                                                | 147 |

| 6.4 Execution time ratio of META-1Q and GDS-JOIN using FP16 over mixed FP16-FP32 on a selection of datasets presented in Tables 6.1 and 6.2. . . . .                                                                                                                                                                                                                | 154 |

| 6.5 Execution time of GDS-JOIN, META-1Q and META-16Q using mixed FP16-FP32, and GDS-JOIN and TED-JOIN using FP64, on a selection of datasets (Table 6.1 and 6.2. META-1Q and META-16Q are using the dataset reordering optimization. . . . .                                                                                                                        | 155 |

## LIST OF ABBREVIATIONS AND DEFINITIONS

### Abbreviations

**AMX** Advanced Matrix Extensions

**ASIC** Application-Specific Integrated Circuit

**AVX** Advanced Vector Extensions

**CPU** Central Processing Unit

**CUDA** Compute Unified Device Architecture

**DBSCAN** Density-Based Spatial Clustering of Applications with Noise

**FP16** Half-precision floating-point format using 16 bits

**FP32** Single-precision floating-point format using 32 bits

**FP64** Double-precision floating-point format using 64 bits

**GPGPU** General-purpose computing on Graphics Processing Units

**GPU** Graphics Processing Unit

**ILP** Instruction-Level Parallelism

**$k$ -NN**  $k$ -Nearest Neighbors

**MMA** Matrix Multiply-Accumulate

**RT** Ray-tracing

**SIMD** Single Instruction Multiple Data

**SIMT** Single Instruction Multiple Threads

**TC** Tensor Core

**WMMA** Warp Matrix Multiply-Accumulate

## Definitions

**Candidate point** Point to which we compute the distance to a query point to determine if it is within a search threshold.

**Catastrophic cancellation** Extreme loss of precision when subtracting two nearby floating point numbers or when adding two nearby floating point numbers of opposite signs. This issue is more likely to happen when using lower precision data types, such as data types stored using 16 bits.

**Clustering** Application that groups objects together.

**CUDA** API designed by Nvidia to give programmatic access to their GPUs.

**CUDA Cores** Smallest compute unit of Nvidia GPUs.

**Distance similarity join** Algorithm finding all pairs of points that are within a distance  $\epsilon$  from each other.

**DBSCAN** Clustering algorithm identifying an unspecified amount of clusters that have a minimum density, and discarding points considered as noise.

**Global memory** Dedicated off-chip GPU memory, with the largest capacity but also highest bandwidth and latency than other GPU memories.

**Heterogeneous computing** Involves concurrently using different architectures (e.g., CPU and GPU) for computing a single problem. We consider here that heterogeneous computing requires the CPU to act as more than just a host for the GPU.

**Host** Role endorsed by the CPU when also using a GPU. Its role consists of allocating memory on the GPU, initiating the memory transfers between the CPU and GPU, start the kernels, etc. A host is mandatory when using the GPU.

**ILP** Instruction-Level Parallelism, ability for a processor's core to compute several independent instructions at once, such as an addition and a multiplication on different variables.

**Indexing** Method used to store objects usually based on their spatial coordinates. Indexing structures are then used to efficiently retrieve specific points (typically candidate points), and can greatly reduce the number of points to search compared to brute-force searches.

**Kernel** Function instantiated by the host and executed on the GPU.

**$k$ -NN** Algorithm finding the  $k$  nearest neighbors of a query point, according to a distance measure.

**Main memory** RAM available to the CPU.

**Query point** The point being searched within a given algorithm.

**Range query** Ensemble of the distance calculations between a query point and its candidate points.

**Ray Tracing Cores** Type of specialized GPU core designed to improve the performance of ray tracing. These units are designed to efficiently search Bounding Volume Hierarchy trees and compute intersection operations.

**Search-and-refine** Execution model where an index is searched for each query point to prune their search space and reduce the number of candidate points. The candidate points are then refined to compute the actual result.

**SIMD** Single Instruction Multiple Data, a parallel execution model where multiple threads execute the same instruction, but on different data elements. SIMD is also possible on a single thread when using vectorized instructions.

**SIMT** Single Instruction Multiple Threads, a parallel execution model used by GPUs, where the same instruction is executed concurrently by the threads of a warp.

**Tensor Cores** Type of specialized GPU core designed for Matrix Multiply-Accumulate (MMA) operations.

**Thread divergence** Occurs when GPU threads of a warp do not follow the same path in the instruction control flow, such as in conditional statements. Branches are executed sequentially, reducing the overall parallelism and thus performance.

**Warp** Group of 32 GPU threads that execute the same instruction, and which is defined in hardware.

**WMMA** Warp Matrix Multiply-Accumulate, library provided by Nvidia giving a programmatic access to the Tensor Cores. This also describes a computing model, where a GPU warp calculates a matrix-multiply accumulate operation, where two matrices are multiplied and a third matrix is added to the result.

## PREFACE

This dissertation contains four peer-reviewed publications. We summarize these publications as follows:

- Chapter 3: Benoit Gallet and Michael Gowanlock, Load Imbalance Mitigation Optimizations for GPU-Accelerated Similarity Joins, *IEEE High-Performance Big Data, Deep Learning, and Cloud Computing Workshop (HPBDC), Proceedings of the 2019 IEEE International Parallel and Distributed Processing Symposium Workshops (IPDPSW)*, pages 396–405, 2019, doi: 10.1109/IPDPSW.2019.00078. *Note: This paper won the best paper award at the High-Performance Big Data and Cloud Computing Workshop.*

- Chapter 4:

- Benoit Gallet and Michael Gowanlock, HEGJoin: Heterogeneous CPU-GPU Epsilon Grids for Accelerated Distance Similarity Join, *Proceedings of the 25<sup>th</sup> International Conference on Database Systems for Advanced Applications (DASFAA)*, pages 372–388, 2020, doi: 10.1007/978-3-030-59419-0 23.

- Benoit Gallet and Michael Gowanlock, Heterogeneous CPU-GPU Epsilon Grid Joins: Static and Dynamic Work Partitioning Strategies, *Data Science and Engineering*, volume 6, pages 39–62, 2020, doi: 10.1007/s41019-020-00145-x.

- Note that we include in this dissertation the extended journal version of the conference paper.

- Chapter 5: Benoit Gallet and Michael Gowanlock, Leveraging GPU Tensor Cores for Double Precision Euclidean Distance Calculations, *Proceedings of the 29<sup>th</sup> IEEE International Conference on High Performance Computing, Data, and Analytics (HiPC)*, pages 135–144, 2022, doi: 10.1109/HiPC56025.2022.00029.

Chapter 6 is formatted as a conference paper, but has not been accepted for publication yet.

# Chapter 1

## Introduction

In recent years, there has been a need to process or analyze large volumes of data using efficient algorithms. Similarity searches are one such algorithm that is often employed to process large datasets, and are widely used in various fields such as image [30] and document similarity [12], or data clustering [19, 20, 32]. More generally, similarity search algorithms are typically used to find objects in a dataset that are similar to a given query object, and according to a given metric. The similarity between two objects corresponds to their computed distance, and two objects are considered similar if their distance is within a certain threshold, which is defined by the user and may vary depending on the use case. Using traditional processing techniques, which are typically sequential by default, severely limit the performance of similarity search algorithms.

Parallel computing consists of processing several tasks or a task on different data at the same time and is an efficient solution to improve similarity search algorithms performance. By breaking down their execution into smaller tasks and executing them concurrently on multiple processing units, whether using Central Processing Units (CPUs) or Graphics Processing Units (GPUs), we can significantly improve the performance of similarity search algorithms, and can process increasingly larger datasets as well. Despite being designed for graphic applications, GPUs recently emerged as a more efficient solution for parallel processing than CPUs, in part thanks to their substantially higher core count and much higher memory bandwidth. More generally, parallel computing is essential to improve the perfor-

mance of many algorithms, or to allow the processing of larger datasets while yielding a practical execution time.

Similarity search algorithms benefit greatly from parallel processing techniques, as their overall computation often consists of many smaller operations that can be done in parallel, and that therefore scale well with the increased core counts of GPUs compared to CPUs. Additionally, as these algorithms typically process large volumes of data, the higher memory bandwidth of GPUs compared to the system’s main memory accessed by the CPU, also helps improve the performance of similarity search algorithms. Consequently, we observe in the literature that GPUs have been gradually more used to implement similarity search algorithms, and are often more efficient than previously proposed algorithms using CPUs.

Many data analysis algorithms, including similarity search algorithms, use the Euclidean distance formula to measure the similarity between pairs of objects [12, 19, 20, 21, 24, 32, 46, 57, 82, 91]. The Euclidean distance measures the straight-line distance between two objects according to their spatial coordinates, and is not constrained by the number of data dimensions. When many objects are processed, computing Euclidean distances can be a major performance bottleneck, which needs to be addressed. Given a dataset  $V$ , computing the similarity between all objects has a time complexity of  $O(|V|^2)$  [31]. In the literature, many published works propose to reduce this complexity by reducing the number of distance calculations computed, particularly by using an indexing data structure. Such data structures index data, typically based on their spatial coordinates, which allows for fast data retrieval. More particularly, and depending on the search threshold, indexes ensure that some points can not be within that threshold of a query point, thus typically reducing the overall number of distance calculations to compute, and therefore reducing the overall time complexity of the algorithm. We identify two types of indexing structures, based on trees [13, 14, 16, 17, 33, 48, 87], and grids [21, 22, 45, 46, 57]. Due to the curse of dimensionality [15, 50, 51], many of the indexing structures are efficient only in low or high dimensionality. Furthermore, because these indexing structures are designed for either

the CPU or the GPU, and because of the differences between CPU and GPU architectures, algorithms using these structures on the CPU will not perform well on the GPU, and vice versa.

In the literature, the majority of proposed distance similarity search algorithms, or algorithms employing Euclidean distance calculations, examine the CPU as the target platform. With the recent introduction of General Purpose Computing on Graphics Processing Units (GPGPU), GPUs have been increasingly used for a wide range of applications thanks to their significantly greater throughput than CPUs: GPUs typically have several orders of magnitude more cores than CPUs, and their onboard global memory bandwidth is also several times greater than the main memory (RAM). However, where CPU cores can compute independently, the Single Instruction Multiple Thread (SIMT) architecture of GPUs imposes groups of 32 threads to execute the same instruction at a time. Consequently, some algorithms may not perform well when executed on the GPU, particularly algorithms with data dependencies or those with a task-parallel division of work. In the case of Euclidean distances, computing the distance between two objects is independent of computing the distance between two other objects. Thus, computing Euclidean distances is a highly parallel calculation scaling well with the number of threads/cores used. As such, GPUs with thousands of cores are excellent architectures for improving the performance of Euclidean distance calculations, and other algorithms that employ them, including distance similarity searches.

While CPU architectures have not extensively changed in recent years, each consecutive generation of GPU is significantly different and much faster than the previous generation. In particular, the Volta generation of Nvidia GPUs [71] introduced Tensor Cores (TCs). TCs are an Application-Specific Integrated Circuit (ASIC) designed to exclusively compute Matrix Multiply-Accumulate operations, at a much higher throughput than general-purpose CPU or GPU CUDA cores. Given four matrices  $A, B, C$  and  $D$ , TCs compute  $D = A \times B + C$ , with a significantly greater throughput than general-purpose cores.

*Note that the GPU-related research was conducted using Nvidia GPUs and the Nvidia CUDA API. As such, we use the corresponding terminology throughout this dissertation. Nevertheless, the GPU concepts we discuss in this dissertation are relevant to other modern GPUs as well, and only the terminology may differ.*

## 1.1 Motivations

The performance of data-analysis algorithms is directly dependent on the input data characteristics: the number of objects, their distribution in the data-space, data dimensionality, among other factors. To process increasingly larger datasets in a reasonable amount of time, improving the algorithms is necessary, and the improvements should be able to exploit newer hardware features and, overall, all computational capabilities of a computer platform. The literature regarding Euclidean distance calculation and distance similarity searches has several shortcomings that motivated the work conducted in this dissertation, which we detail below.

- Many research works focus on using either the CPU or the GPU. While focusing on a single architecture makes optimizing algorithms relatively easier, this leaves one or the other architecture underutilized: CPU algorithms do not leverage GPUs by default; GPU algorithms sporadically need to use the CPU as a host for the GPU, essentially performing tasks such as transferring data from main memory (RAM) to the GPU’s global memory, and vice versa. As compute clusters and consumer-grade computers are increasingly equipped with GPUs [89], algorithms designed for either the CPU or the GPU would not be able to efficiently leverage all the computational power of such platforms.

- Parallel CPU and GPU algorithms are notoriously challenging to design and optimize. Furthermore, because of all the architectural differences between CPUs and GPUs, efficient optimizations working well on the CPU may not work as well on the GPU,

and vice versa. In particular, algorithms with irregular workloads can have a negative impact on the performance, particularly on the GPU because of the SIMD execution model. Distance similarity searches, when using an indexing structure, are an algorithm with such irregular workloads: all the objects may not compare to the same number of objects, where each object may have a different workload. On the SIMD architecture of the GPU, it might yield lower resource usage, as threads with lower workloads might wait on threads with a higher workload to finish their assigned work, effectively reducing the overall parallelism of the algorithm, and thus performance.

- GPU architectures have greatly evolved, and even recent algorithms may not leverage the full capabilities of recent GPUs, or recent features may not be an obvious choice when designing an algorithm for the architecture. TCs fall into this category: fields related to machine learning or more generally to linear algebra extensively use TCs, with groundbreaking efficiency. On the other hand, very few general scientific applications have leveraged TCs to improve their performance, leaving a part of the compute resource unused.

- A CPU algorithm and a GPU algorithm that have the same purpose, e.g., computing  $k$ NN searches, may have different workloads depending on how the algorithms are implemented, usually to fit the targeted architecture. When targeting both the CPU and GPU, this workload disparity is likely to make it more difficult to optimally assign the work to the processors: an input object may have a different workload depending on if the CPU processes it, or if the GPU does.

## 1.2 Challenges

Efficiently computing Euclidean distances and distance similarity searches on different architectures can be challenging. In particular, we identify the following challenges that must be resolved:

- The architecture of the CPU and GPU are very different, and an algorithm designed for the CPU is likely to perform poorly on the GPU, and vice versa. Leveraging both the CPU and GPU at the same time thus requires careful considerations to achieve the best performance.

- GPU architectures are greatly evolving, and are becoming heterogeneous: along with the general-purpose cores, recent GPU architectures are also equipped with cores for a specific purpose, such as TCs. Because these two types of cores serve a different purpose, leveraging them both concurrently also requires particular considerations, similarly to leveraging the CPU and GPU at the same time.

- Algorithms with irregular workloads such as distance similarity searches are more challenging to optimize than algorithms with regular workloads. Irregular workloads between GPU threads lower the overall parallelism, and thus performance, of an algorithm.

### 1.3 Contributions

This dissertation makes the following contributions, aiming at solving the challenges described above:

- Using an existing state-of-the-art GPU distance similarity search algorithm as a baseline, we identify a major bottleneck regarding the irregular workloads that we solve by reordering the way objects are processed and how objects are assigned to threads, effectively increasing resource usage and performance.

- We combine the previously optimized algorithm and a state-of-the-art parallel CPU distance similarity search algorithm to propose a heterogeneous CPU-GPU algorithm, where both architectures are concurrently used and perform similar tasks (i.e., both the CPU and GPU search an indexing data structure, compute Euclidean distances,

etc.). This CPU-GPU algorithm was able to achieve similar or better performance than CPU-only and GPU-only algorithms in most experiments.

- We propose several Euclidean distance calculation algorithms leveraging TCs, which can then be used in other algorithms such as distance similarity searches. By using TCs, we achieve better performance than when using general-purpose CPU or GPU cores.

- While still a work in progress, we investigate leveraging both the general-purpose GPU cores and TCs. By using both types of cores, we expect to make better use of the available resources and to improve the performance compared to algorithms using only one or the other type of core.

*Distance similarity searches and, more generally Euclidean distance calculations, are omnipresent in many data analysis algorithms, where they are often responsible for producing the greatest. While most of the literature focuses on optimizing an algorithm for a specific architecture, this may leave other processors of a different architecture unused in a given computer platform. Leveraging all available architectures, including CPUs, general-purpose GPU cores and specific-purpose GPU TCs is essential for improving the overall performance of distance-centric algorithms, and to make better use of available computational resources.*

## 1.4 Outline

This dissertation is outlined as follows: we introduce in Chapter 2 general background necessary for the rest of the dissertation. We then present in Chapter 3 through Chapter 6 the different contributions we make. We finally conclude the dissertation in Chapter 7, where we propose several future research directions as well.

## Chapter 2

### Background and Related Work

We give in this chapter important background material relevant to the rest of the dissertation. Note that there is substantial overlap with the background sections of subsequent chapters. Furthermore, because Chapters 3-6 are self-contained published or ready to submit papers, some notations used in this section may be inconsistent throughout the dissertation, for which we apologize to the reader.

#### 2.1 Euclidean Distance

Let  $V$  be a dataset in  $d$  dimensions, where for a point  $p \in V$ ,  $p_i$  is the  $i^{th}$  point in  $V$  where  $i = 1, \dots, |V|$ , and  $p_i(j)$  is the  $j^{th}$  coordinate of  $p$  where  $j = 1, \dots, d$ . Given two points  $a, b \in V$ , the Euclidean distance formula calculates the distance between the points  $a$  and  $b$  as follows:

$$dist(a, b) = \sqrt{\sum_{j=1}^d (a(j) - b(j))^2}. \quad (2.1)$$

The Euclidean distance function is a fundamental operation in many data analysis algorithms, and is heavily used for distance similarity searches [19, 20, 21, 32, 42, 46, 57, 82]. As such, the algorithms that we optimize and that we propose in this dissertation use this function (Equation 2.1) as well. Additionally, we use in Chapters 5 and 6 an expanded form of the Euclidean distance formula:

$$dist(a, b) = \sqrt{\sum_{j=1}^d a(j)^2 - 2a(j)b(j) + b(j)^2} \quad (2.2)$$

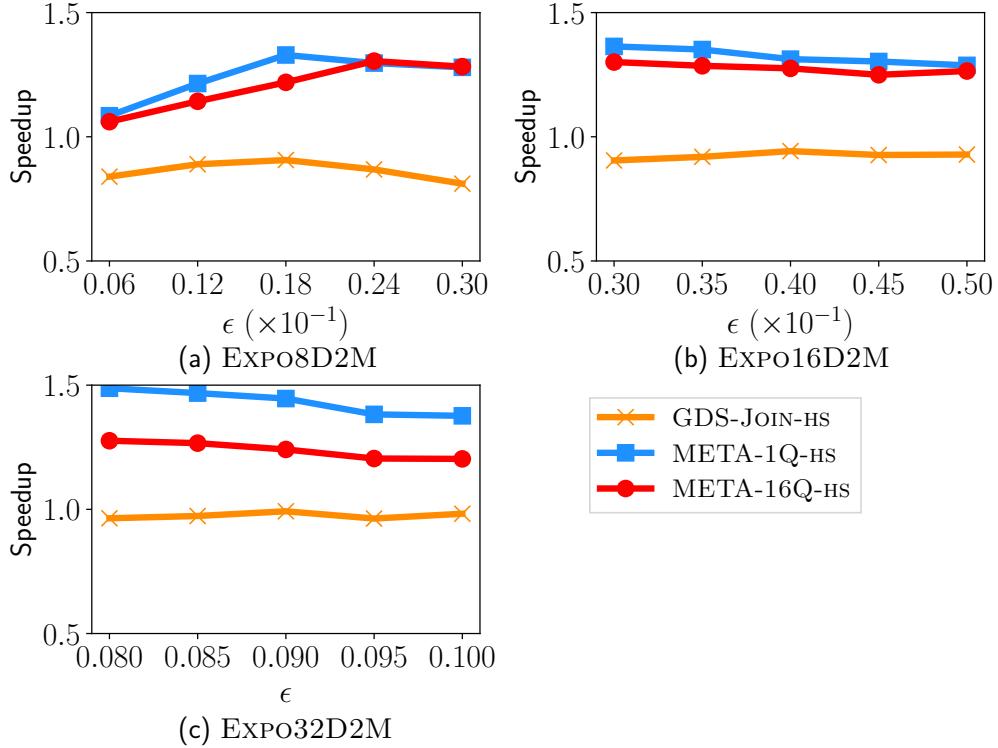

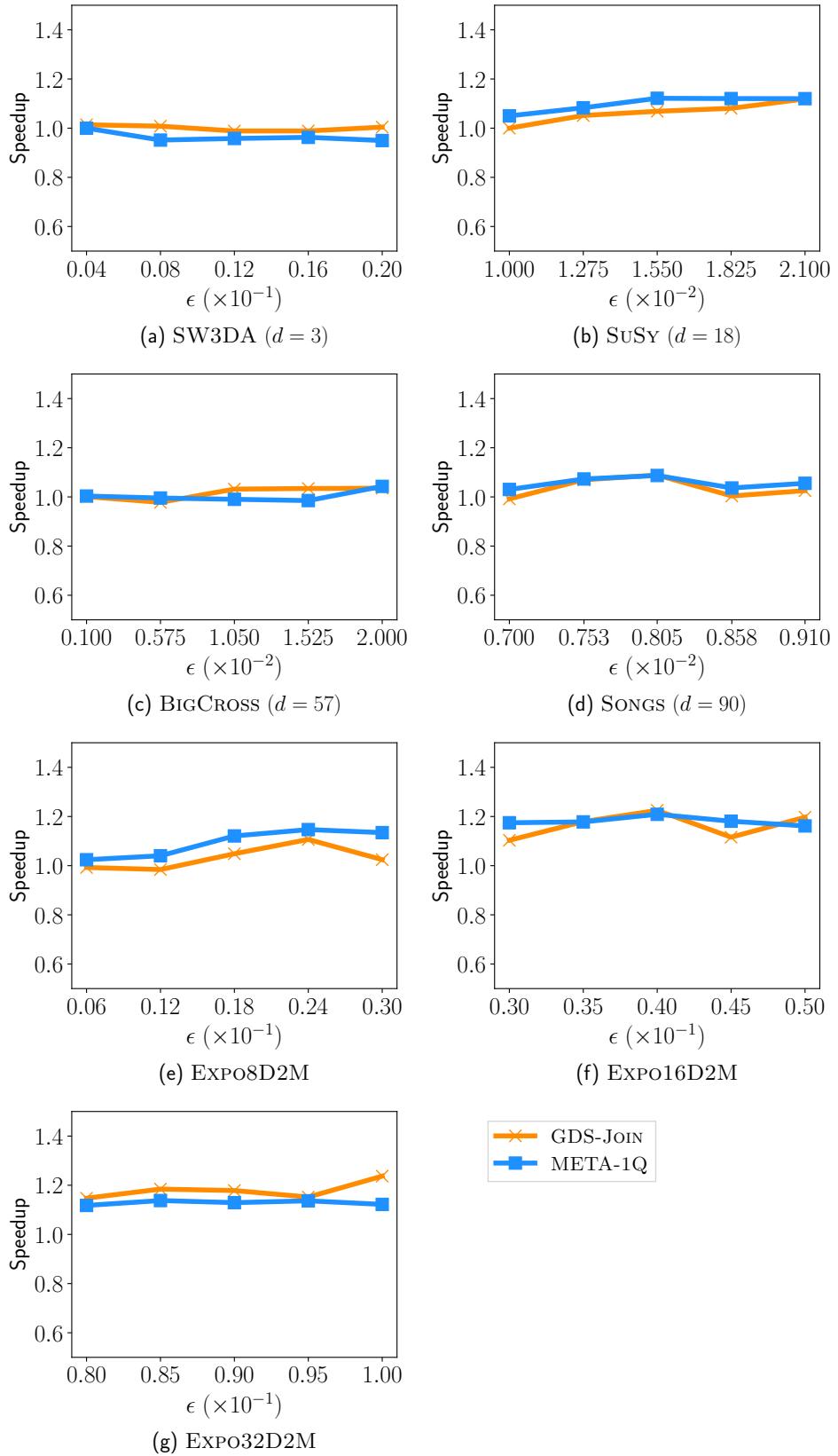

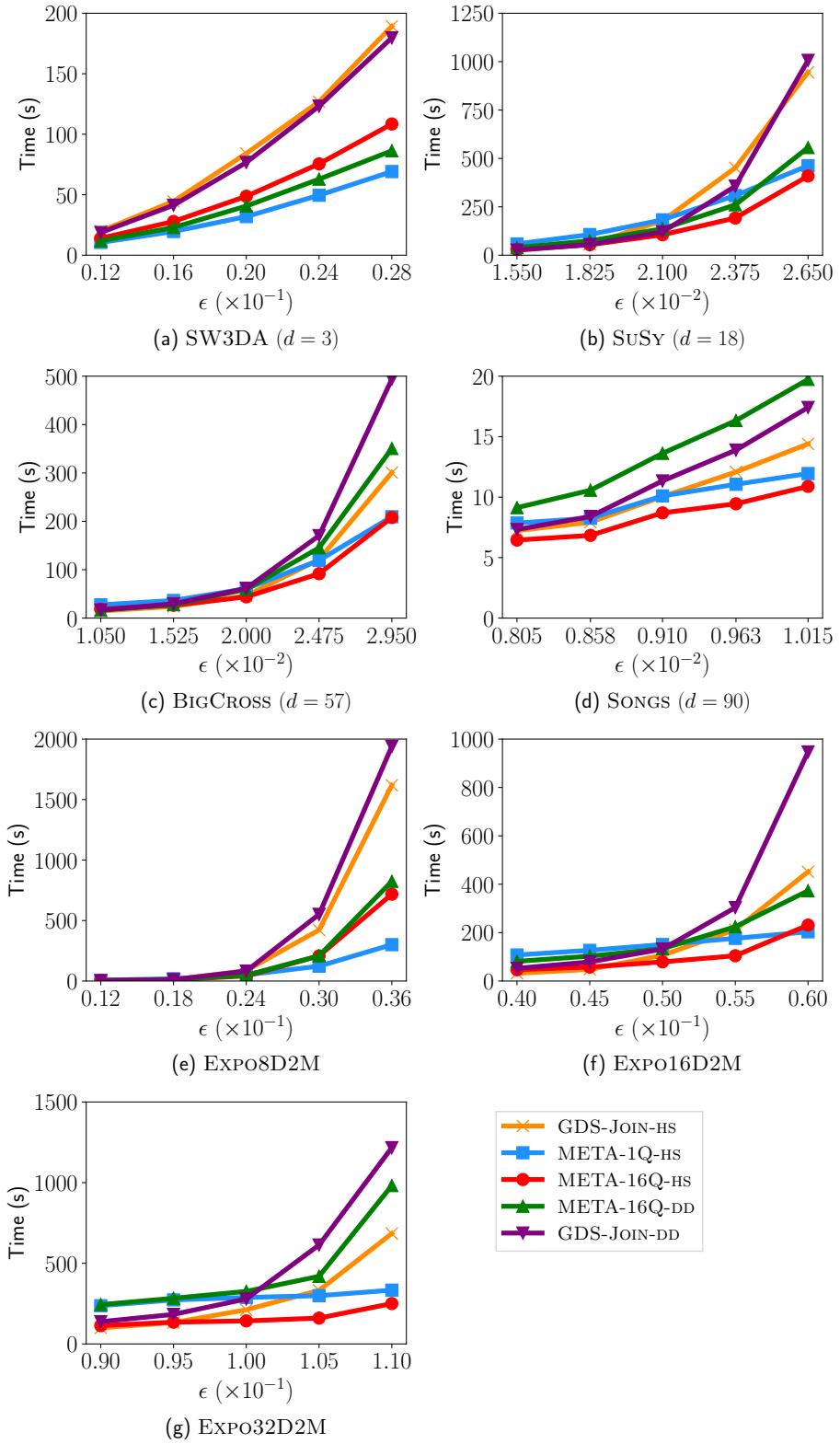

## 2.2 Distance Similarity Searches